Thách thức

- Hiện nay tốc độ phát triển của linh kiện bán dẫn là rất nhanh, yêu cầu ngày càng cao kéo theo đó mức độ phức tạp theo cấp số nhân. Việc tích hợp thiết kế và xác minh chip AI là cực kỳ phức tạp và là thách thức lớn

- Sự khó khăn và cần thiết tạo ra các chiplet AI NPU hiệu suất cực cao thế hệ tiếp theo

Quá trình phát triển AI NPU của ETRI

Vào năm 2019 nhóm thiết kế bộ xử lý AI NPU tại Viện nghiên cứu AI quốc gia của ETRI đã phát triển bộ xử lý AI đầu tiên của Hàn Quốc với tên gọi AB9. Một bộ xử lý điện toán mạng nơ-ron nhân tạo Floating 16 bit FP16. AB9 đã được một số công ty thương mại áp dụng thành công cho các máy chủ điện toán AI của họ.

Sau thành công đó, nhóm thiết kế bộ xử lý AI NPU đã tìm cách đẩy ranh giới của AI xa hơn nữa bằng cách sử dụng chiến lược thiết kế dựa trên chiplet để tạo ra bộ xử lý thần kinh ABS1 (NPU) – thế hệ bộ xử lý AI tiếp theo của họ. ETRI muốn tận dụng khả năng của công nghệ đóng gói IC 3D để tăng đáng kể băng thông và hiệu suất trong khi giảm công suất và chi phí cho các thiết kế ASIC hiệu suất cao, phức tạp của họ.

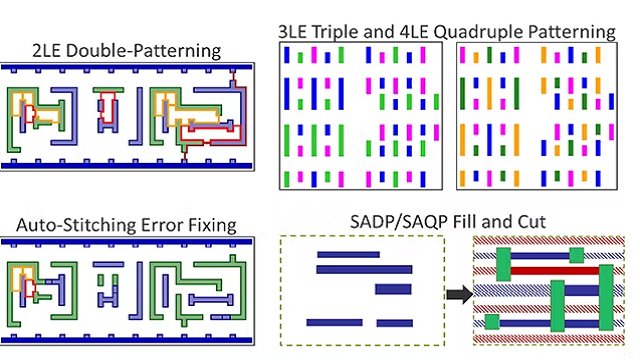

Động lực đổi mới của ETRI hoạt động trong một bối cảnh lớn hơn, trong đó ngành công nghiệp bán dẫn phải đối mặt với thách thức về mặt công nghệ đáng kể khi chi phí cao hơn, năng suất thấp hơn và các hạn chế về kích thước lưới bắt buộc. Nhu cầu về các giải pháp khả thi cho kiến trúc hệ thống trên chip (SoC) thay thế đơn khối truyền thống. Điều này đang thúc đẩy một xu hướng mới nổi là phân tách các chức năng của thiết bị thành các khối IP rắn, chế tạo được triển khai tại các node quy trình hay còn gọi là công nghệ Chiplet.

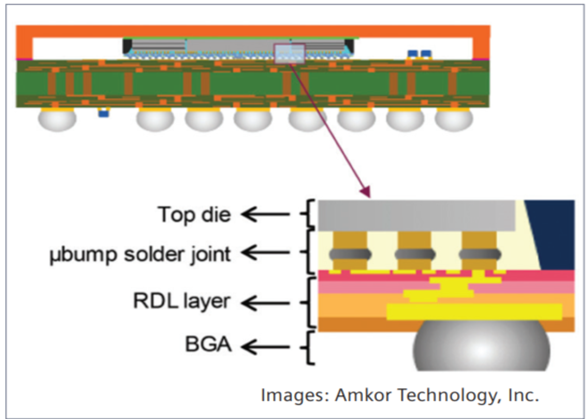

Nhiều chiplet, bộ nhớ và một thiết bị ASIC tùy chọn, tùy chỉnh có thể được gắn và kết nối với nhau thành một gói duy nhất bằng cách sử dụng các giao diện chiplet-to-chiplet tốc độ cao, băng thông rộng, chẳng hạn như các giao diện sử dụng thông số kỹ thuật Bunch of Wires (BoW) và Universal Chiplet Interconnect Express (UCIe). Việc lắp ráp IC 3D không đồng nhất có thể mang lại kết quả hiệu suất cao hơn với chi phí thấp hơn và năng suất cao hơn, với diện tích chỉ lớn hơn một chút so với SoC đơn khối truyền thống.

3D IC heterogeneously integrated assembly

3D IC heterogeneously integrated assembly

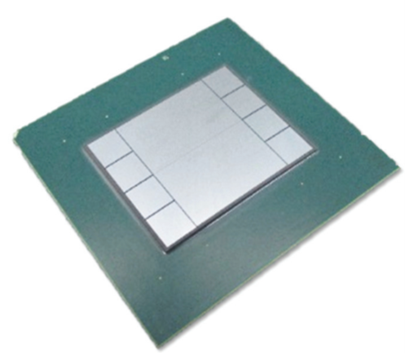

ETRI cũng muốn thiết kế tốc độ cao có thể tự hào về hiệu quả năng lượng tiên tiến và hiệu suất AI cao hơn. Để đạt được những mục tiêu này, ABS1 tích hợp hai chiplet AI NPU với tám ngăn xếp bộ nhớ HBM3. Mười trong số các khuôn này được tích hợp trên một lớp phân phối lại (RDL) interposer quy mô lớn. Kết quả sẽ là bộ xử lý AI petaflops đầu tiên có hiệu quả năng lượng rất cao.

ETRI đã hợp tác với Amkor để giải quyết các vấn đề kỹ thuật như độ cong vênh mất cân bằng, độ ổn định nhiệt và khả năng sản xuất quy mô lớn bộ Interposer. ETRI hợp tác với Amkor Technology Korea với tư cách là đối tác thiết kế và OSAT của họ cho ABS1. Bộ RDL của Amkor phù hợp với việc sản xuất quy mô lớn interposer, hỗ trợ tích hợp chiplet với chi phí thấp và đáp ứng các yêu cầu cụ thể của ETRI.

Giải pháp của Siemens

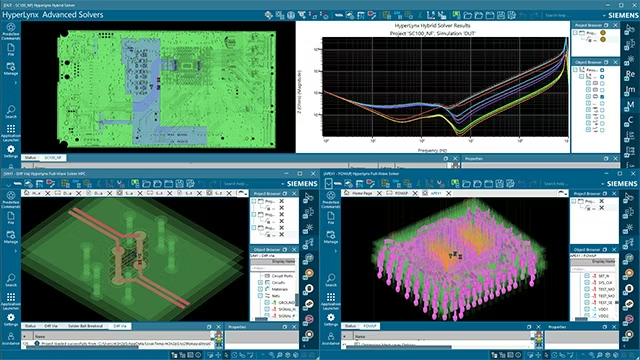

Siemens là đối tác tin tưởng và lâu dài của Amkor, cũng như khả năng của giải pháp đóng gói tiên tiết của Siemens, Amkor và ETRI đã chọn Xpedition Package Designer (XPD), Xpedition Substrate Intergrator (xSI) và Calibre 3DSTACK để giúp họ thiết lập một phương pháp tiếp cận có hệ thống để thiết kế công cụ lý tưởng AI NPU dựa trên Chiplet.

Amkor Korea đã sử dụng XPD vì khả năng thiết kế và hiệu suất tuyệt vời của nó, mà họ cần để xử lý các thiết kế gói tiên tiến mật độ cao của họ, chẳng hạn như bộ xen kẽ RDL. Hơn nữa, đối với thiết kế của chính bộ xen kẽ RDL, XPD chứa các chức năng đặc biệt giúp giảm thời gian chu kỳ thiết kế. Amkor ban đầu đã áp dụng XPD cho Công nghệ Fan-out tích hợp wafer silicon (SWIFT) của họ cho phép tạo ra các cấu trúc 3D tiên tiến, chẳng hạn như các bộ xen kẽ RDL và các thiết kế gói tiên tiến.

“Siemens IC packaging design tools helped us provide a fast and highquality design service to our customers even with large body and chiplet package structures”

JaeBeom Shim

Package Design Manager – Amkor Korea

Các tính năng khác mà XPD có lợi thế là chức năng “physical reuse circuit” của nó, đóng vai trò đặc biệt quan trọng trong việc giảm tổng thời gian chu kỳ thiết kế và chức năng xuất trực tiếp GDS thực sự của XPD. Khả năng tạo hình mặt phẳng động hiệu suất cao của nó là một phần lớn lý do tại sao họ chọn XPD cho thiết kế đóng gói IC kích thước lớn và bộ xen kẽ RDL.

Ngoài ra, Amkor có rất nhiều kinh nghiệm sử dụng xSI để trực quan hóa và tối ưu hóa kết nối bump trong quá trình tích hợp nhiều die. xSI đã chứng minh cho thấy khả năng thiết kế vượt trội ngay cả khi xử lý số lượng bump lên đến hàng trăm nghìn.

xSI được tích hợp nhiều tính năng cho phép Amkor tích hợp các cấu trúc thiết kế cấp độ 3DSTACK cho cả bộ xen kẽ RDL và chất nền. xSI có thể dễ dàng thực hiện tối ưu hóa kết nối bump cần thiết để đạt được thiết kế bộ xen kẽ RDL chất lượng tốt hơn, điều này thực sự đã được xSI thực hiện thành công trên bộ xen kẽ. Amkor đã chạy thành công xác minh 3DSTACK Calibre cho các thiết kế gói tiên tiến mật độ cao, vì vậy họ biết rằng đây là lựa chọn tốt cho dự án bộ xử lý AI NPU của ETRI.

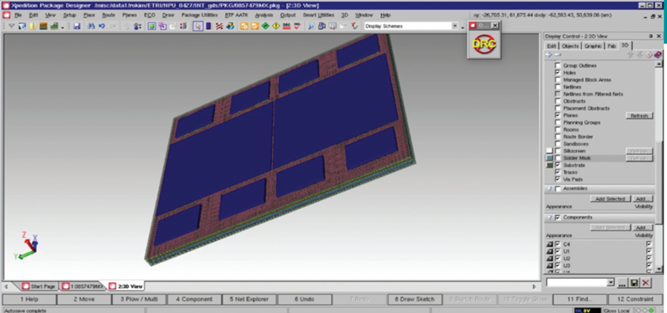

The ABS1 NPU being designed in Xpedition Package Designer by the Amkor advanced IC packaging design team (source: Amkor Technology)

The ABS1 NPU being designed in Xpedition Package Designer by the Amkor advanced IC packaging design team (source: Amkor Technology)

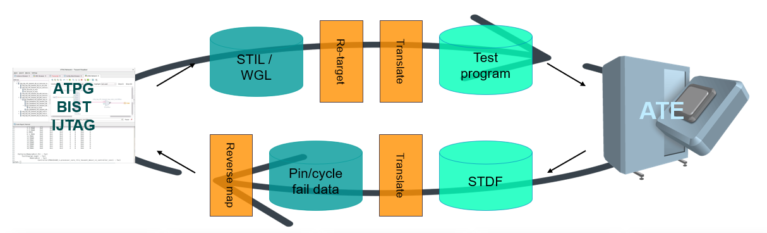

ETRI ban đầu tập trung vào việc xây dựng một luồng CAD VLSI liền mạch cho đóng gói tiên tiến, sử dụng xSI để mô tả kiến trúc chiplet cấp cao nhất của ABS1 NPU bao gồm nhiều khuôn, chiplet và ngăn xếp HBM3. Bằng cách cung cấp mô tả này về kiến trúc chiplet hàng đầu, xSI sau đó cho phép họ chuyển sang môi trường công cụ mô phỏng kiến trúc, Xpedition Package Designer (xPD), để thiết kế chất nền đóng gói và interposer.

Khi họ bắt đầu thiết kế bộ xen kẽ RDL, netlist thông tin về khuôn NPU và khuôn HBM chỉ có trong Verilog. Vì vậy, họ cần Siemens cung cấp các công cụ có thể hình dung các kết nối bump-to-bump và micro-bumps-to-C4-bumps, bao gồm gói BGA. Thật vậy, xSI không chỉ có khả năng hình dung kết nối mà còn tối ưu hóa các kết nối. ETRI rất hài lòng với cách xSI thực hiện các chức năng này.

Amkor cũng cần xác minh các kiểm tra kết nối của kiến trúc đa khuôn, bộ xen kẽ RDL và chất nền gói trong các gói nâng cao mật độ cao, phân cấp của ETRI. Tất cả các kiểm tra này đã được thực hiện thành công bằng cách sử dụng luồng xác minh xSI-Calibre 3DSTACK, tạo ra danh sách mạng cấp nguồn và kiểm tra kết nối giữa các cấu trúc đa die, bộ xen kẽ và chất nền gói.

“Amkor has successfully provided package designs from RDL interposer to substrate.We also verifed the connectivity and performed DFM with xSI and Calibre 3DSTACK. Siemens IC packaging design tools helpedus provide a fast and high-quality design service to our customers even with large package and chiplet package structures,”

JaeBeom Shim, the Amkor package design manager in Korea reports.

Vào cuối công việc thiết kế, ETRI đã hoàn thành thành công việc xác minh 3DSTACK cho cả bộ xen kẽ và gói 3D IC.

The final ABS1 device is the first petaflops AI processor with very high energy efficiency (source: Amkor Technology)

The final ABS1 device is the first petaflops AI processor with very high energy efficiency (source: Amkor Technology)

Tham khảo thêm:

Liên hệ với Vietbay để được tư vấn: