Quá trình đưa mạch tích hợp (IC) vào hoạt động bao gồm nhiều vòng lặp qua các bước khác nhau, trải dài từ thiết kế, DFT (Design for Test – Thiết kế để kiểm tra) đến các lĩnh vực kiểm thử. Khi DFT ngày càng phức tạp, việc gỡ lỗi trở nên thách thức hơn. Tuy nhiên, với Tessent SiliconInsight, một sản phẩm của Siemens EDA, các kỹ sư có thể thực hiện việc xác minh sau sản xuất (post-silicon validation), chẩn đoán và phân tích lỗi của IC một cách nhất quán và hiệu quả.

Tessent SiliconInsight: Giải pháp mạnh mẽ cho xác minh hậu silicon và chẩn đoán lỗi

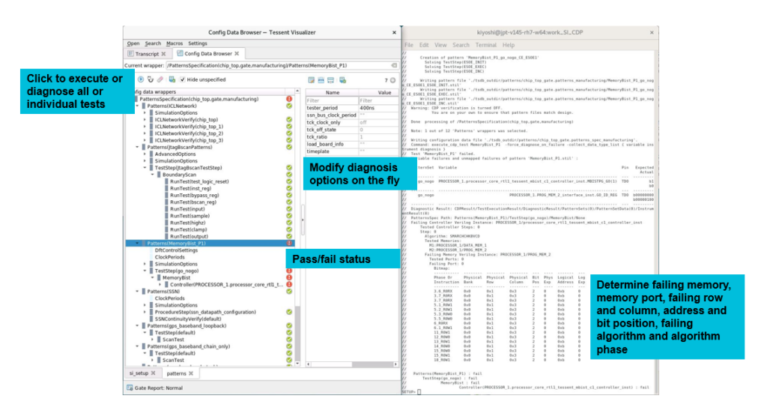

Tessent SiliconInsight cung cấp cho người dùng một giải pháp toàn diện để gỡ lỗi và kiểm tra các mạch tích hợp (IC) trong quá trình đưa vào hoạt động trên silicon. Công cụ này cho phép truy cập thời gian thực vào các tín hiệu trên chip và các nút bên trong, giúp các kỹ sư quan sát hành vi của mạch trong quá trình hoạt động. Bằng cách nhanh chóng xác định và định vị các lỗi sản xuất có thể tồn tại trong IC, Tessent SiliconInsight có thể cải thiện quy trình kiểm tra và nâng cao tỷ lệ sản phẩm đạt chuẩn trong các lần sản xuất sau, dẫn đến sản phẩm đáng tin cậy và tiết kiệm chi phí hơn.

Hỗ trợ toàn diện từ môi trường Tessent Shell và các công nghệ kiểm tra tích hợp

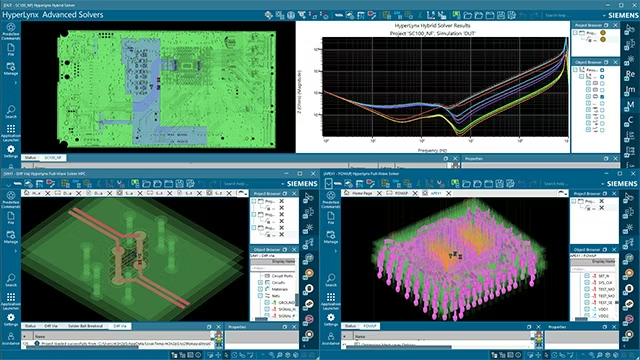

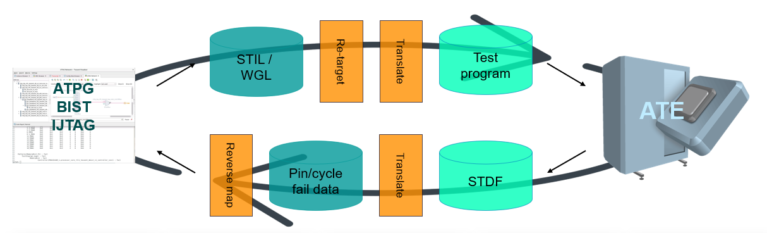

Tessent SiliconInsight hoạt động trong môi trường Tessent Shell, cung cấp cho người dùng một môi trường thống nhất để đưa mạch vào hoạt động trong các môi trường mô phỏng, trên máy tính bàn, và trong sản xuất. Người dùng có thể dễ dàng chuyển đổi giữa các môi trường này, điều này rất quan trọng để gỡ lỗi và kiểm tra IC một cách hiệu quả. Công cụ này bao gồm hỗ trợ cho ATPG (Automatic Test Pattern Generation – Tạo mẫu kiểm tra tự động), LBIST (Logic Built-In Self-Test – Kiểm tra tích hợp tự động logic), MBIST (Memory Built-In Self-Test – Kiểm tra tích hợp tự động bộ nhớ), và IJTAG (Internal JTAG – JTAG nội bộ) tương tác, cung cấp một giải pháp toàn diện cho việc gỡ lỗi và kiểm tra IC.

Dựa trên TSDB (Tessent Shell DataBase), SiliconInsight có khả năng chẩn đoán lỗi logic xuống các flop bị lỗi, đồng thời tạo một dofile dành cho Tessent Diagnosis. Dofile này có thể được thực thi ngay trong cùng một phiên làm việc (yêu cầu giấy phép Tessent Diagnosis) để thực hiện chẩn đoán chi tiết tới mức net (yêu cầu mô hình thiết kế phẳng) hoặc polygon (yêu cầu cơ sở dữ liệu layout). Chẩn đoán MBIST và ATPG cũng có thể được thực hiện tương tác trên máy kiểm tra (tester) thông qua ATE-Connect. Ngoài ra, chẩn đoán hàng loạt (volume diagnosis) có thể được thực hiện bằng cách chạy các mẫu kiểm tra từ một gói CDP (Characterization and Debug Package) đã được tạo trước, sau đó xử lý hậu kỳ các nhật ký lỗi từ máy kiểm tra ở chế độ offline.

Tính năng vượt trội của Tessent SiliconInsight Desktop trong môi trường thử nghiệm

Ngoài ra, tùy chọn SimDUT (Simulation Device Under Test) hỗ trợ việc xác minh trước silicon (pre-silicon validation) cho quy trình chẩn đoán (và công cụ SiliconInsight) của một thiết kế. Chức năng này yêu cầu sử dụng một công cụ mô phỏng Verilog từ EDA, cũng như mô hình mô phỏng Verilog của thiết kế (và thư viện đi kèm). Người dùng có thể chèn lỗi vào thiết kế, chạy thử nghiệm trên SiliconInsight, quan sát lỗi xuất hiện, và sau đó thực hiện chẩn đoán.

Tessent SiliconInsight Desktop cung cấp nhiều tính năng vượt trội, cho phép người dùng kiểm tra các thiết bị trong môi trường thử nghiệm “bench-top”. Công cụ này hỗ trợ xác định các flop bị lỗi trong các thiết kế TestKompress, ánh xạ lỗi tới các core trong các thiết kế phân cấp (hierarchical designs), thực hiện đặc tả thiết kế (ví dụ: phân tích đường dẫn quan trọng – critical path analysis), tối ưu hóa mẫu kiểm tra (ví dụ: công suất dịch chuyển/tần suất chuyển đổi – shift power/toggle rate), và thực hiện chẩn đoán lỗi có nhận thức layout (layout-aware defect diagnosis).

(Nguồn: Siemens)

Tham khảo thêm:

Liên hệ với Vietbay để được tư vấn: