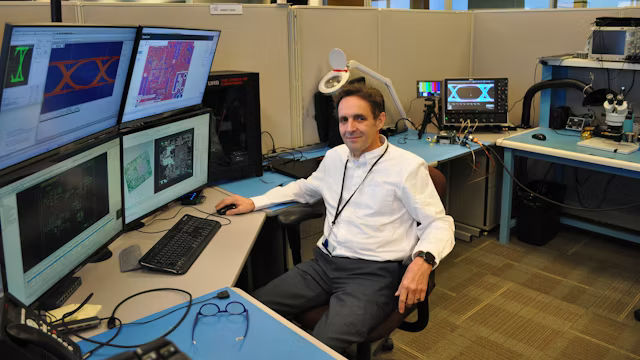

The bring-up process of integrated circuits (ICs) involves several iterations through multiple steps spanning design, DFT (Design for Test), and test domains. As DFT becomes more complex, debugging becomes even more challenging. However, with Tessent SiliconInsight, a product offered by Siemens EDA, engineers can perform post-silicon validation, diagnosis, and failure analysis of ICs in a consistent and efficient manner.

Tessent SiliconInsight: A Powerful Solution for Post-Silicon Validation and Fault Diagnosis

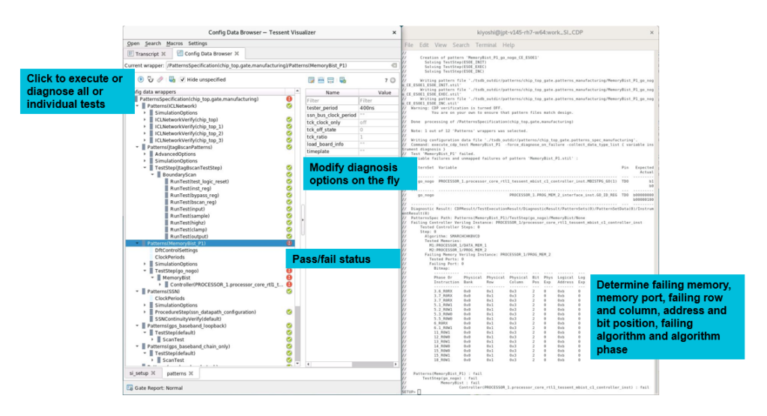

Tessent SiliconInsight provides users with a comprehensive solution for debugging and testing ICs during the silicon bring-up process. The tool enables real-time access to on-chip signals and internal nodes, allowing engineers to observe the behavior of the circuit in operation. By quickly identifying and locating manufacturing defects that may exist within an IC, Tessent SiliconInsight can refine the test process and improve the yield of future production runs, ultimately leading to a more reliable and cost-effective product.

Comprehensive Support from Tessent Shell Environment and Integrated Testing Technologies

Tessent SiliconInsight operates within the Tessent Shell environment, providing users with a consistent bring-up environment in simulation, desktop, and production test environments. Users can switch between these environments quite easily, which is essential for debugging and testing ICs efficiently. The tool covers ATPG (Automatic Test Pattern Generation), LBIST (Logic Built-In Self-Test), MBIST (Memory Built-In Self-Test), and interactive IJTAG (Internal JTAG) support to provide a comprehensive solution for IC debugging and testing.

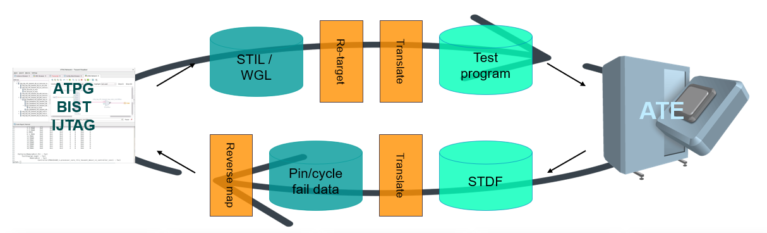

Based on the TSDB (Tessent Shell DataBase), SiliconInsight can diagnose logic failures to failing flop(s), and also generate a dofile for Tessent Diagnosis. This dofile can be executed in the same session (which will require a Tessent Diagnosis license) to run diagnosis down to the net (requires a flat design model) or polygon (requires a layout database). MBIST and ATPG Diagnosis can also be done on the tester interactively through ATE-Connect, and volume diagnosis can be done by running test patterns from a pre-generated CDP (Characterization and Debug Package) and post-processing failure logs from the tester offline.

Outstanding Features of Tessent SiliconInsight Desktop in Testing Environments

In addition, the SimDUT (Simulation Device Under Test) option facilitates pre-silicon validation of the diagnosis flow (and SiliconInsight) for a design. This functionality requires use of an EDA Verilog simulation tool, as well as a Verilog simulation model of the design (and library). A user can inject failures, run the test on SiliconInsight, see the test fail, and run diagnosis.

Tessent SiliconInsight Desktop offers even more capabilities, allowing users to test devices in an accessible bench-top environment, find failing flops for TestKompress designs, map failures to core(s) for hierarchical designs, perform design characterization (e.g. critical path analysis), pattern optimization (e.g. shift power/toggle rate), and run layout-aware defect diagnosis.

(Source: Siemens)

Read more:

Contact us for free and detailed advice: