Tại hội nghị User2User Châu Âu năm 2023, Artur Jutman, Giám đốc Testonica, trình bày một quy trình làm việc dựa trên Tessent để triển khai hệ thống tham chiếu dựa trên FPGA nhằm đánh giá và xác thực tiền silicon của IJTAG infrastructure mục tiêu cũng như xác thực hệ sinh thái công cụ sẽ được được sử dụng trong sản xuất hoặc trong quá trình bảo trì.

Bài thuyết trình đã được ghi lại và hiện có sẵn cho mọi người xem.

Tessent IJTAG

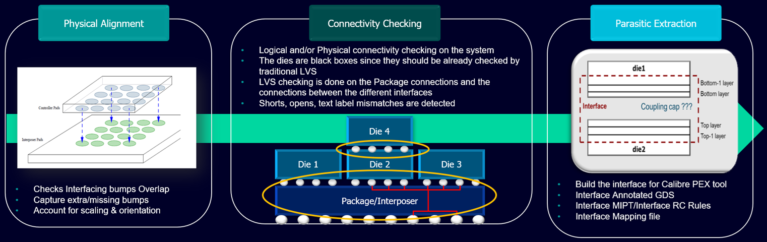

Những người chủ chốt trong ngành bán dẫn đang đẩy nhanh việc áp dụng IEEE Std. 1687 (còn gọi là IJTAG) với sự trợ giúp của công cụ hỗ trợ EDA hoàn thiện. Tessent IJTAG của Siemens EDA là một trong những giải pháp tiên phong mở đường cho những người áp dụng sớm và ngày nay cung cấp một hệ sinh thái thiết bị đo nhúng và DFT đầy đủ tính năng dựa trên tiêu chuẩn IJTAG.

Trong bài trình bày này, Jutman mô tả cách họ sử dụng Tessent để triển khai hệ thống tham chiếu dựa trên FPGA để đánh giá và xác thực tiền silicon của IJTAG infrastructure mục tiêu cũng như xác thực hệ sinh thái công cụ sẽ được sử dụng trong sản xuất hoặc trong quá trình bảo trì. Hệ thống thu được là một thiết kế HDL được triển khai bên trong logic có thể cấu hình lại của FPGA. Thiết kế này chứa hàng chục thiết bị được tích hợp vào mạng IJTAG, do đó có thể truy cập được thông qua cổng truy cập thử nghiệm JTAG FPGA tiêu chuẩn. Mặc dù nền tảng này được triển khai trên FPGA nhưng nó vẫn cung cấp khả năng tương tự để hoạt động với IJTAG giống như trên ASIC có hỗ trợ IEEE 1687.

Network IJTAG

Network IJTAG được triển khai có nhiều lớp phân cấp và sắp xếp các thiết bị thành bốn mạng con có cấu trúc liên kết kết nối khác nhau. Mạng cung cấp quyền truy cập đọc/ghi hoặc chỉ đọc vào các thanh ghi bên trong (một số tài nguyên có mục đích chung và một số tài nguyên tích hợp như cảm biến điện áp và nhiệt độ trên chip) cũng như các thiết bị hướng ra ngoài được kết nối với đèn LED bên ngoài và công tắc trên bảng. Thiết kế được viết bằng ngôn ngữ VHDL, tổng hợp bằng chuỗi công cụ Xilinx Vivado, mô phỏng trong môi trường ModelSim và được xác thực bằng Tessent.

Các mô-đun của IJTAG network được mô tả ở định dạng IEEE 1687 ICL (Instrument Connectivity Language) tiêu chuẩn cũng như cấu trúc kết nối mạng được tạo từ HDL. Một bộ quy trình PDL (Procedural Description Language) cũng đã được chuẩn bị; mỗi PDL có IEEE Std được định mục tiêu lại tương ứng. Các mẫu 1149.1 (JTAG). Các mẫu này nhắm vào cổng 1149.1 TAP của FPGA, được mô tả trong mô-đun ICL trên cùng của IJTAG network. Điều này cho phép sử dụng các công cụ JTAG tiêu chuẩn từ nhà cung cấp ưu tiên và đánh giá các công cụ đó trong bối cảnh hoạt động của IJTAG. Nghiên cứu điển hình này là kết quả của sự hợp tác giữa Testonica và ADVANTEST. Buổi nói chuyện sẽ xem xét lại công việc đã làm và những bài học kinh nghiệm.

Liên hệ với Vietbay để được tư vấn trực tiếp