Arm and Technology Entitlement in Chip Design

Arm is a market leader in semiconductor IP, including interconnect technologies that serve as the backbone of many system-on-chips (SoCs). Part of the success of their processing chips lies in achieving technology entitlement. At the last User2User conference, Arm principal engineer John Mitchell described technology entitlement as more than just chip performance; it means getting the most out of a given design technology. In addition to the key metrics in IC place-and-route—performance, power, and area (PPA)— technology entitlement at Arm includes being able to get the most optimal performance, power and area per unit micron during design implementation.

Interconnect Design Challenges

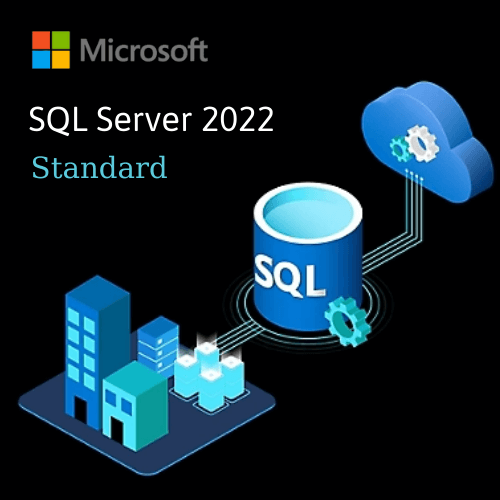

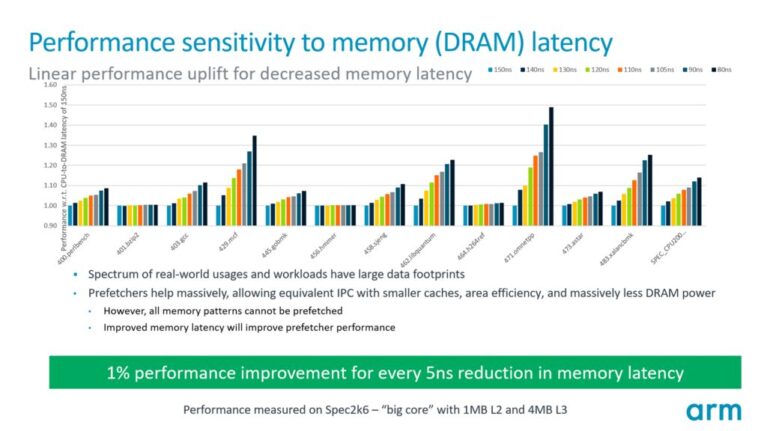

The topic of technology entitlement in Mitchell’s presentation led to a discussion around the challenges of their interconnect designs. They found that the interconnect performance has a significant impact on the system in which it operates. “For various workloads, every 5 ns of latency we can reduce in the interconnect, we get a 1% performance increase in our CPU core,” Mitchell said. This is illustrated in Figure 1.

Figure 1. Performance measured on SPEC2k6 – “big core” with 1 MB and 4 MB L3.

Figure 1. Performance measured on SPEC2k6 – “big core” with 1 MB and 4 MB L3.

Arm offers solutions for optimizing interconnect designs, and they have been using a hand-crafted method to achieve technology entitlement. However, to realize their hopes for improved time to market, they need a fully automated place-and-route solution that understands interconnect designs.

Siemens Aprisa Solution

This is where Aprisa enters the story. Arm began a trial of the Aprisa IC place-and-route tool from Siemens, and looked at how Aprisa resolved a few key implementation challenges, including:

- Global register placement

- Global routing and track assignment to reduce SI

- Co-optimizing buffer/layer/NDR

Mitchell said they had just taped out a test chip for the Morello program demonstrator, which aims to develop a more secure hardware architecture for processors. The SoC, however, was in a different technology, with different options and interconnect, and was optimized differently. Therefore, all of the technology investigation, the design investigation and the setup had to be redone to build this system which proved to be the perfect case to see how long it would take to do in their current methodology, vs with Aprisa, and find out if the Siemens solution could match their results.

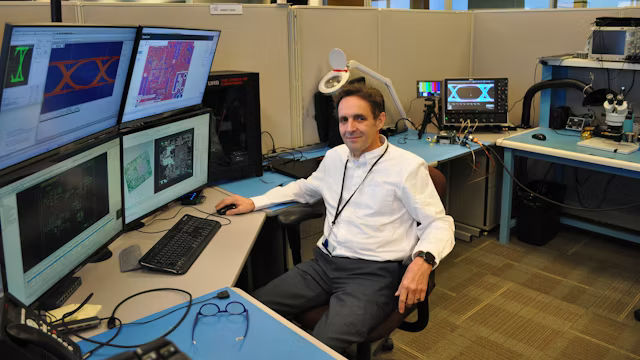

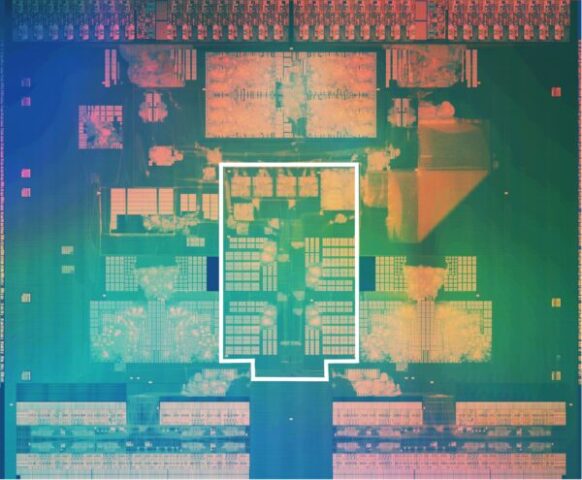

Aprisa was used on the top-level interconnect; about 1.5 million placeable instances. “We didn’t want to just look at the high level and say, yes, it was able to close timing. We wanted to see if it had a proper understanding of the technology and was able to capitalize on it in the way we can with our hand-crafted methods,” said Mitchell. Figure 2 shows the SoC.

Figure 2. Arm chip.

Figure 2. Arm chip.

Results from Using Aprisa

Results were better than expected. The global placement was similar to Arm’s traditional results, but Aprisa made better use of the available space given that the modules were not constrained to specific bounding boxes, and it could spread some key logic producing a somewhat more refined result. The Aprisa global routing and track assignment resulted in lower net capacitance and significantly less signal integrity issues.

“Overall, Aprisa achieved 90% of technology entitlement at the push of a button,” said Mitchell.

The Aprisa team takes pride in the out-of-the-box experience. The software comes with a reference flow, is easy to use and easy to customize. A built-in design wizard helps with initial design setup and scripting customization. Aprisa is certified for advanced process nodes from the major foundries, including the TSMC N5/N4 processes.

Arm plans future trials with Aprisa to match what they get from their hand-crafted flow at the most advanced nodes, and to explore routing for power reduction.

(Source: Siemens)

Read more:

Contact us for free and detailed advice: