At the 2023 European User2User conference, Artur Jutman, Director at Testonica, presents a workflow based on Tessent to implement an FPGA-based reference system for pre-silicon evaluation and validation of a target IJTAG infrastructure as well as validation of the tool ecosystem to be used in production or during in-field maintenance.

The presentation was recorded and is now available for anyone to view.

Key players in the semiconductor industry are accelerating their adoption of IEEE Std. 1687 (aka IJTAG) with the help of maturing EDA tool support. Tessent IJTAG from Siemens EDA is amongst the pioneering solutions that paved the way to early adopters, and today provides a full-featured DFT and embedded instrumentation ecosystem based on the IJTAG standard.

Tessent to implement an FPGA-based reference system

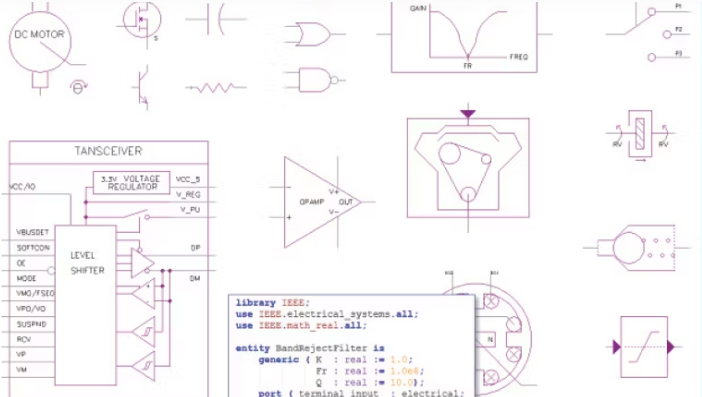

In this presentation, Jutman describes how they used Tessent to implement an FPGA-based reference system for pre-silicon evaluation and validation of a target IJTAG infrastructure and validation of the tool ecosystem to be used in production or during in-field maintenance. The resulting system is an HDL design implemented inside the reconfigurable logic of an FPGA. The design contains several dozen instruments integrated into an IJTAG network, which in turn is accessible through a standard FPGA JTAG test access port. Even though the platform is implemented on FPGA, it provides the same ability to work with IJTAG in as if it were on an ASIC with IEEE 1687 support.

IJTAG network

The implemented IJTAG network has multiple layers of hierarchy and arranges the instruments into four sub-networks of various interconnection topology. The network provides read/write or just read access to internal registers (some general-purpose and some built-in resources such as on-chip temperature and voltage sensors) as well as outwards-oriented instruments connected to external LEDs and switches on the board. The design is written in VHDL language, synthesized using Xilinx Vivado toolchain, simulated in ModelSim environment and validated with Tessent.

The modules of the IJTAG network are described in the standard IEEE 1687 ICL (Instrument Connectivity Language) format as well as the network interconnect structure generated from HDL. A set of PDL (Procedural Description Language) procedures was also prepared; each PDL has their respective re-targeted IEEE Std. 1149.1 (JTAG) patterns. These patterns target the FPGA’s 1149.1 TAP port, which is described in the topmost ICL module of the IJTAG network. This enables usage of standard JTAG tools from a preferred vendor and the evaluation of those tools in the context of IJTAG operations. This case study is a result of collaboration between Testonica and ADVANTEST. The talk will review the work done and the lessons learned.

Source: Siemens

Vietbay, an authorized distributor of Siemens EDA and a comprehensive strategic partner of Siemens DISW in Vietnam, is proud to be the coordinating unit to organize this important event. With more than 20 years of experience in the field of consulting, providing, and training technology transfer, Vietbay is committed to providing comprehensive IC and PCB design and manufacturing solutions with services and added value. From there, Vietbay helps customers master technology, develop quickly and sustainably in the digital age.

Contact us for free and detailed advice