Introduction

Challenges in GPU Design:

- Modern GPUs need to deliver high performance for applications such as gaming, medical imaging, and industrial design. This requires chips to optimize power to reduce heat, lower system costs, and extend battery life.

- Three main goals:

- Reduce power consumption at peak load.

- Optimize power without affecting the current design process.

- Automate power optimization in the early stages.

RTL Clock Gating and Related Techniques

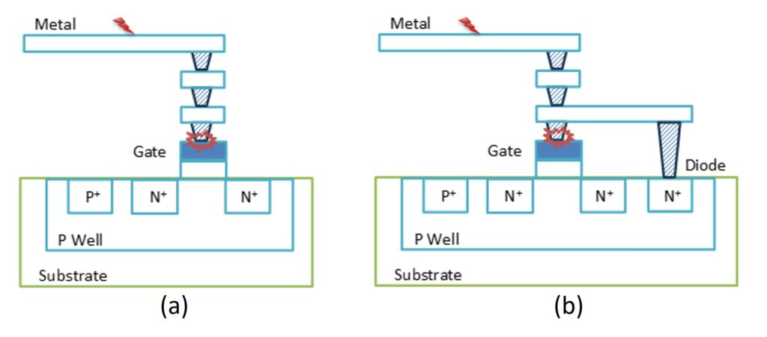

Clock Gating: A technique to reduce dynamic power by disabling clock signals to unnecessary components.

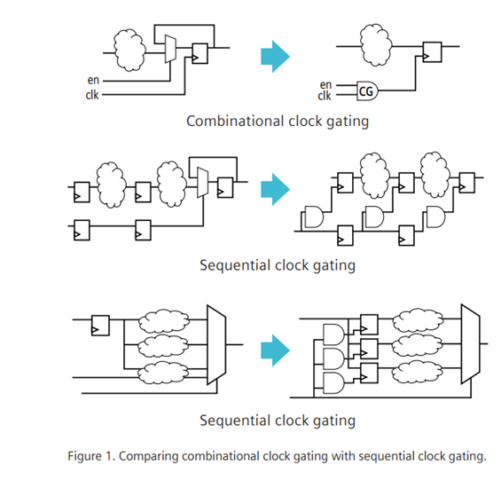

Combinational Clock Gating:

- Easy to implement by replacing logic conditions in RTL with clock gating cells.

- RTL synthesis tools can automatically detect and add these conditions.

Sequential Clock Gating:

- More complex, requiring circuit behavior analysis over multiple cycles.

- Optimizes power by exploiting sequential relationships between registers and data.

Limitations of Manual Clock Gating:

- Time-consuming and labor-intensive to identify optimal conditions.

- Difficult to verify and create functional test cases for hundreds of clock gating conditions.

Integrating PowerPro CG Tool

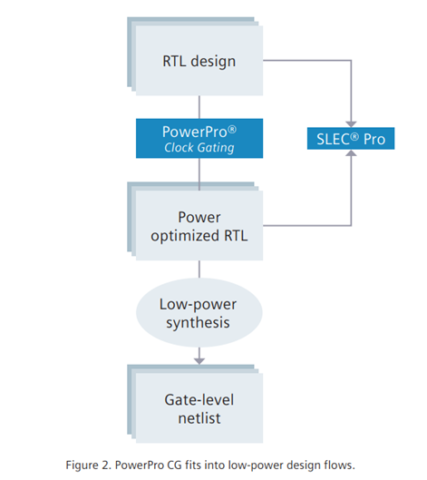

PowerPro CG: An automated power optimization tool based on sequential analysis, enabling:

- Identification of new clock gating conditions missed by manual processes.

- Retention of original RTL code format, including comments and pragmas.

- Integration with SLEC Pro (Sequential Equivalence Checking) to ensure code functionality remains unchanged after optimization.

Effectiveness of PowerPro CG (Siemens EDA)

The tool has been tested across multiple design blocks and delivered significant results:

- Increased the number of clock-gated registers or extended the duration of clock gating.Reduced

- power consumption by 16% to 34.8%, with design area impact below 0.81%.

- Ensured the design still meets timing requirements.

| Design Block | Number of Registers in Original RTL | Clock Gated Registers in Original RTL | % of Clock Gated Registers in Original RTL | Registers Enabled or Enhanced by PowerPro Clock Gating |

| B1 | 34500 | 34233 | 99% | 5722 |

| B2 | 28047 | 23410 | 83% | 4555 |

| B3 | 39032 | 34607 | 89% | 2951 |

Conclusion

- PowerPro CG (Siemens EDA) helps NVIDIA achieve better power optimization solutions compared to traditional manual methods.

- Integrating PowerPro CG into low-power design processes enables effective automation and generates optimized RTL code for synthesis stages.

About Siemens Digital Industries Software

Siemens provides comprehensive software solutions for digitizing design and manufacturing processes, including tools like PowerPro CG and SLEC Pro to support power and functional optimization in hardware design.

Read more:

Contact us for free and detailed advice