Quy trình thiết kế FPGA của bạn đã sẵn sàng cho các thiết kế mới nhắm đến các FPGA phức tạp mới nhất chưa? Bạn đang gặp khó khăn với các công cụ phần mềm không hoạt động cùng nhau? Bạn có thể đạt được mục tiêu QoR trong quá trình phát triển và tối ưu hóa thiết kế trong ngân sách mong muốn không? Nhóm PCB và FPGA có thể cộng tác để đạt được các ràng buộc chung của hệ thống không?

Quy trình thiết kế FPGA hoàn chỉnh của Siemens EDA

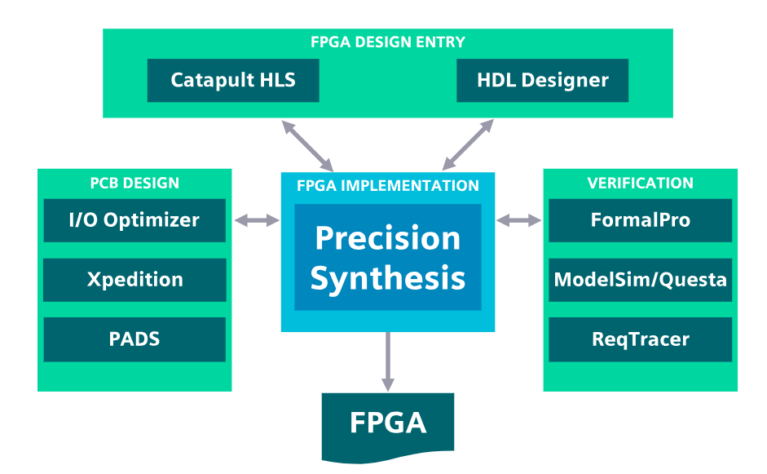

Các giải pháp thiết kế FPGA của Siemens EDA cung cấp nền tảng thiết kế FPGA tích hợp, tổng hợp, xác minh, kiểm tra tương thích. Và thiết kế PCB giúp tăng tốc các thiết kế FPGA từ khâu tạo ra đến bo mạch, đáp ứng các mục tiêu QoR của thiết kế và các yêu cầu ràng buộc hệ thống.

Một nhóm mới các thiết kế FPGA và các phương pháp liên quan

FPGA ngày càng được sử dụng nhiều trong phân khúc thị trường phát triển nhanh (chẳng hạn như 5G, ML và AI) và các thiết kế có độ tin cậy cao/quan trọng – bảo mật. Các thiết kế này yêu cầu sử dụng các phương pháp mới như HLS hoặc SEE. Ngoài ra, nó còn đặt ra những thách thức trong việc gỡ lỗi và xác minh những thiết kế lớn này.

Thiết kế FPGA an toàn và đáng tin cậy

Đối với các thiết kế quan trọng- bảo mật, Precision Hi-Rel cung cấp các cơ chế an toàn (phát hiện, che giấu) để giảm lan truyền lỗi mềm do bức xạ hoặc các điều kiện môi trường khác.

Tăng tốc thiết kế C++/SystemC trên FPGA

Sự tích hợp chặt chẽ và ước tính toán tử số học tốt hơn giữa Catapult và công cụ tổng hợp FPGA Precision rất quan trọng trong việc đạt được QoR tối ưu và thời gian thiết kế cho các thiết kế C++/SystemC.

Mô phỏng cấp cổng có quá chậm không?

Sự tích hợp giữa công cụ tổng hợp FPGA Precision và FormalPro đảm bảo xác minh netlist cấp cổng nhanh hơn dựa trên các thiết kế RTL “golden” với DSP và RAM phức tạp.

Tìm hiểu thêm:

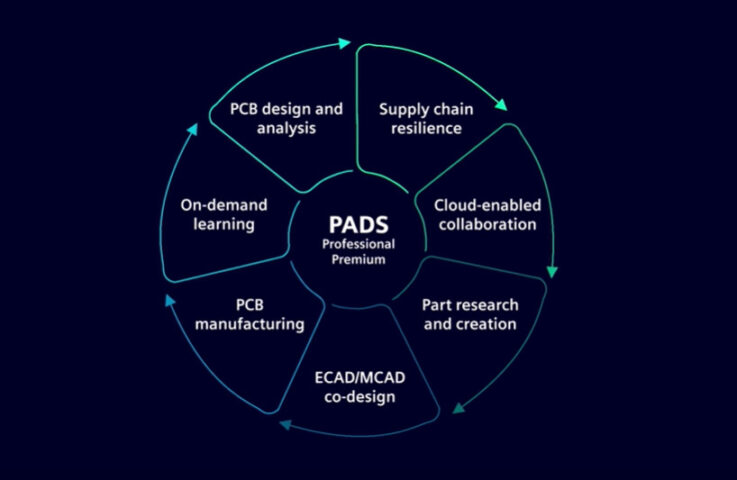

- Đồng thiết kế FPGA/PCB với PADS Professional Premium

- ModelSim – phần mềm xác mình và gỡ lỗi ASIC và FPGA

- Quy trình chuẩn thiết kế trên FPGA

Liên hệ với Vietbay để được tư vấn trực tiếp