Khi độ phức tạp của các thiết kế ngày nay tiếp tục tăng lên, ngày càng có nhiều nhà thiết kế sản phẩm điện tử chuyển sang Field Programmable Gate Arrays (FPGAs) để mang lại nhiều chức năng hơn cho thiết kế PCB.

Lợi ích của việc sử dụng FPGA bao gồm hiệu suất tốt hơn, khả năng lập trình, hiệu quả chi phí, thời gian đưa ra thị trường nhanh hơn và nhiều lợi ích khác. Tuy nhiên, số lượng chân nhiều của các thiết bị này cũng mang đến những thách thức, chẳng hạn như khả năng định tuyến khó khăn, độ dài vết dài hơn, nhiều vias hơn, số lượng lớp tăng lên và các vấn đề về tính toàn vẹn tín hiệu. Khi sử dụng FPGA trong thiết kế, việc thu hẹp khoảng cách giữa các miền FPGA và PCB là rất quan trọng để tối ưu hóa FPGA IO trong bối cảnh của bo mạch.

Tối ưu hóa I/O tích hợp

Điều cần thiết là phải có khả năng tối ưu hóa I/O được tích hợp chặt chẽ với quy trình thiết kế PCB, có thể truy cập được ở bất kỳ giai đoạn nào của dự án.

Điều này bắt đầu với việc định nghĩa thiết bị FPGA. Bằng cách nhóm các chân trên các dãy I/O của FPGA, trình tối ưu hóa mang lại sự linh hoạt hơn trong việc gán chân. Các nhóm này có thể được coi là các thực thể HDL riêng biệt trong công cụ và có thể được tạo thủ công hoặc trích xuất từ tệp HDL (Verilog hoặc VHDL).

Ưu điểm của việc phân vùng chân cắm bao gồm lập kế hoạch kết nối PCB tốt hơn, tạo biểu tượng tùy chỉnh và giảm thiểu các quy tắc hoán đổi chân trong nhóm, dẫn đến kiểm soát tốt hơn việc tối ưu hóa chân và cải thiện việc tháo gỡ mạch.

Việc phân bổ I/O theo quy tắc của nhà cung cấp FPGA theo đúng cấu trúc sẽ giảm thiểu số lần quay lại, trong khi thư viện toàn diện về các thiết bị của nhà cung cấp FPGA giúp giảm thiểu thời gian thiết lập và loại bỏ lỗi thủ công.

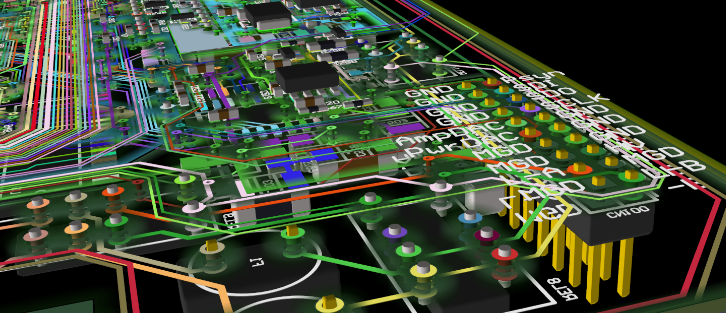

Định tuyến được cải thiện

Một giai đoạn quan trọng của quy trình thiết kế PCB là định vị và định hướng của các thành phần trên bo mạch. Việc sử dụng công cụ lập kế hoạch quy hoạch tích hợp cho phép tối ưu hóa I/O FPGA để cải thiện việc định tuyến. Vì các nhóm/dãy/ I/O đã được xác định nên sau khi các thành phần được định vị, tối ưu hóa IO thực sự sẽ “làm sáng tỏ” các đường dây mạch bằng cách cho phép các chân trong các dãy, được xác định là có thể hoán đổi, thay đổi việc gán chân của chúng. Điều này làm giảm các lớp, giảm thiểu các vấn đề về tính toàn vẹn của tín hiệu, rút ngắn dấu vết và giảm số lượng vias được sử dụng.

Một thư viện toàn diện về các thiết bị của nhà cung cấp FPGA

Thư viện toàn diện về các thiết bị của nhà cung cấp FPGA giúp giảm thiểu thời gian thiết lập và loại bỏ lỗi thủ công. Siemens cung cấp hỗ trợ cho các thiết bị FPGA mới nhất thông qua quan hệ đối tác với các nhà cung cấp FPGA hàng đầu. Nó hỗ trợ đầy đủ các công cụ của nhà cung cấp FPGA sau:

- Altera Quartus II

- Lattice Diamond and ispLEVER

- Microsemi Libero and Designer

- Xilinx ISE and Vivado

Source: Siemens

Liên hệ Vietbay để nhận được các gói ưu đãi đặc biệt: