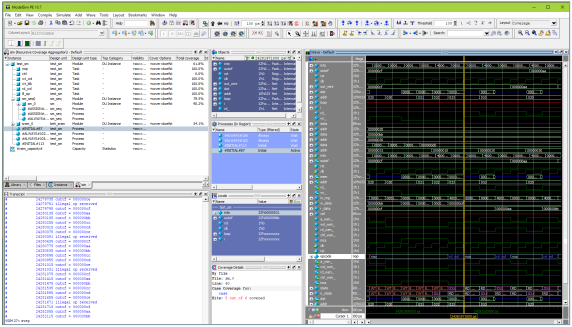

ModelSim mô phỏng hành vi, RTL và gate-level thành code – nhằm mang lại chất lượng thiết kế và năng suất gỡ lỗi cao hơn với trình biên dịch độc lập với nền tảng (platform). Công nghệ Single Kernel Simulator cho phép pha trộn (mixing) VHDL và Verilog trong một thiết kế.

Các tính năng chính

ModelSim tích hợp khả năng xác minh chưa từng có vào một trình mô phỏng HDL hiệu quả về chi phí và phù hợp lý tưởng để xác minh các thiết kế FPGA cỡ nhỏ và vừa – đặc biệt là các thiết kế có chức năng quan trọng, phức tạp.

Bao phủ mã nâng cao

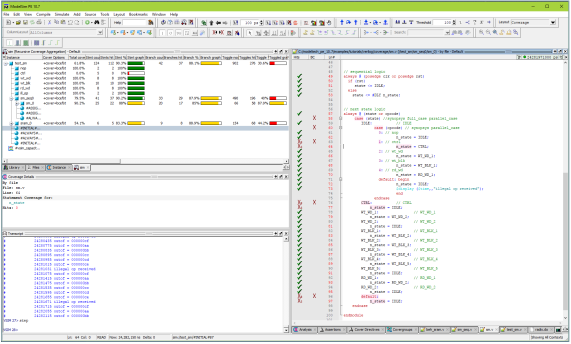

Các khả năng bao quát mã (code coverage) nâng cao của ModelSim cung cấp các số liệu có giá trị để xác minh hệ thống. Ngoài ra, tính dễ sử dụng của ModelSim làm giảm các rào cản đối với việc tận dụng các tài nguyên xác minh. Tất cả thông tin bao phủ được lưu trữ trong cơ sở dữ liệu UCDB hiệu quả cao. Kết quả bao quát có thể được xem một cách tương tác, sau mô phỏng hoặc sau khi hợp nhất nhiều lần chạy mô phỏng.

Mô phỏng HDL hỗn hợp

Hỗ trợ toàn diện Verilog, SystemVerilog cho thiết kế, VHDL và SystemC cung cấp nền tảng vững chắc cho các môi trường xác minh thiết kế đơn và đa ngôn ngữ. Một môi trường thống nhất và dễ sử dụng cung cấp cho các nhà thiết kế FPGA những khả năng nâng cao mà họ cần để gỡ lỗi và mô phỏng.

Môi trường gỡ lỗi trực quan

ModelSim giúp giảm bớt quá trình tìm lỗi thiết kế với môi trường gỡ lỗi được thiết kế thông minh, hiển thị hiệu quả dữ liệu thiết kế để phân tích và gỡ lỗi tất cả các ngôn ngữ mô tả phần cứng. Một loạt các khả năng trực quan cho Verilog, VHDL và SystemC làm cho nó trở thành lựa chọn lý tưởng cho thiết kế ASIC và FPGA.

Để biết thêm thông tin chi tiết, vui lòng liên hệ: