Cách tốt nhất để tạo một System on a Chip (SoC) là với thiết kế IP: các khối thực hiện các chức năng phổ biến như giao diện với các bus tiêu chuẩn (Ví dụ: AMBA® AXI hoặc PCIe). Sau đó, làm thế nào để bạn kiểm tra xem chip có hoạt động với IP không? Bạn cần tạo ra stimulus tuân theo giao thức và cách tốt nhất để xác minh thiết kế của bạn là sử dụng Verification IP hoặc VIP.

Siemens Questa Verification IP (QVIP) có sẵn cho nhiều loại giao thức như AXI, AHB, PCIe/NVMe, Ethernet, USB, Serial, cùng với bộ nhớ DRAM và Flash. QVIP hoạt động với cả thiết kế SystemVerilog và VHDL, đồng thời dễ dàng tích hợp vào testbench UVM.

Quy trình tích hợp QVIP

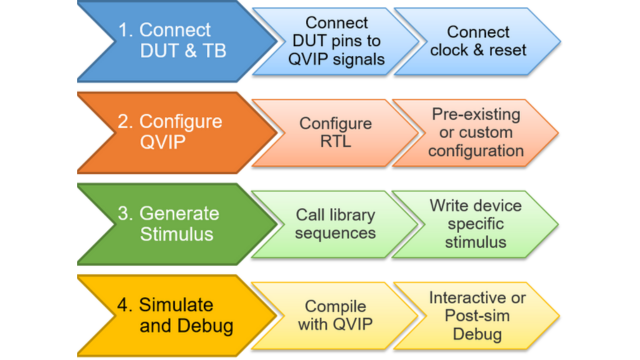

Dưới đây là 4 bước để kết nối Questa Verification IP với testbench. Phần tốt nhất là bạn có thể thực hiện 3 bước đầu tiên bằng công cụ QVIP, Configurator, công cụ này cũng tạo các tệp cho bước cuối cùng.

Bước 1

Trình Configurator đọc netlist và tạo biểu tượng sơ đồ. Bạn kết nối nó với các khối QVIP chẳng hạn như AXI master, cùng với đồng hồ và thiết lập lại. Mã QVIP, bao gồm mô hình chức năng bus và SystemVerilog Assertions nằm trong một mô-đun duy nhất, giúp giảm số lượng kết nối.

Bước 2

Bus RTL của bạn rộng bao nhiêu? QVIP nên hoạt động như thế nào với các tính năng giao thức như tín hiệu RLAST trong AXI? Chỉ định những chi tiết này trong Configurator, bắt đầu bằng cấu hình có sẵn hoặc giá trị tùy chỉnh của riêng bạn.

Bước 3

Questa Verification IP đi kèm với một thư viện các trình tự có thể ngẫu nhiên hóa cho nhiều giao thức để giúp bạn bắt đầu nhanh chóng, cùng với một API đọc/ghi chung để tạo stimulus cụ thể cho thiết kế của bạn.

Bước 4

Configurator tạo ra một testbench và netlist UVM hoàn chỉnh cùng với các tập lệnh và các tệp hỗ trợ cho tất cả các trình mô phỏng chính. Bạn có thể gỡ lỗi tương tác hoặc sau khi mô phỏng hoàn tất. QVIP tạo nhiều tệp nhật ký để bạn có thể nhanh chóng xem các giao dịch cấp cao cũng như các tín hiệu dành riêng cho giao thức cấp thấp.

Để biết thêm thông tin chi tiết, vui lòng liên hệ: