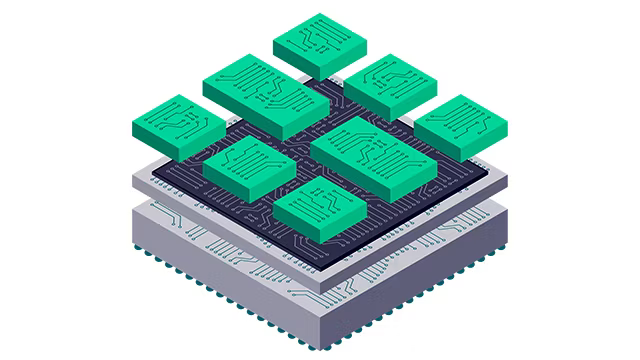

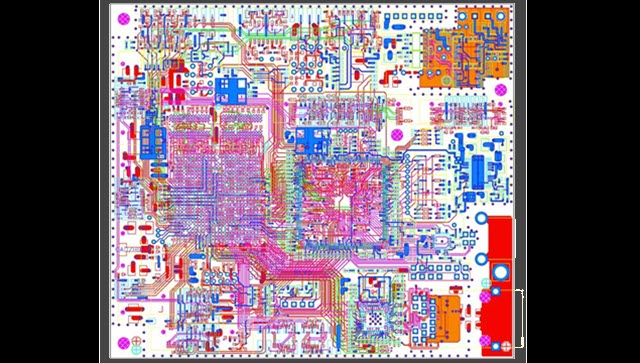

As the semiconductor industry continues to push the boundaries of innovation, the need for advanced 3D IC design solutions has become increasingly critical. 3D IC designs will power the next-generation of semiconductor design and foster AI innovation. Siemens EDA, as a member of the 3DFabric Alliance, is proud to collaborate with TSMC to address the challenges and opportunities presented by this emerging technology.

At the recent TSMC Open Innovation Platform (OIP) symposium, John Ferguson, a senior product management director for Calibre, discussed the company’s latest collaboration with TSMC on 3D IC design enablement. This partnership aims to provide designers with the tools and technologies needed to create complex, high-performance 3D ICs.

Siemens EDA supports TSMC’s 3Dblox

3Dblox is a standard developed by TSMC to streamline and modularize the design of 3D ICs. It’s unified framework for representing the physical and logical aspects of 3D IC designs helps designers work with different 3D IC configurations and technologies. By standardizing the design flow, 3Dblox accelerates the development of advanced 3D ICs and reduce time-to-market. TSMC is working with IEEE to make 3Dblox a publicly available standard, which will further boost growth in the 3D IC design ecosystem. Siemens EDA fully supports TSMC’s 3Dblox platform through our advanced 3D IC design tools and methodologies.

The future of 3D IC design

As AI chips become larger and more complex, the industry requires a collaborative approach to advance 3D IC design. By working together, TSMC and Siemens EDA are committed to addressing the challenges and seizing the opportunities presented by the 3D IC market. This partnership will help shape the future of semiconductor design and enable the development of groundbreaking innovations. “The opportunity and challenge of the true 3D IC market is daunting. It will take both TSMC and Siemens, and frankly the rest of the semiconductor ecosystem, for us to be successful,” – John Ferguson.

(Source: Siemens)

Read more:

Contact us for free and detailed advice: