Discover the optimal solution for verifying SoC connectivity with the Questa Formal Connectivity Check tool, helping Microsemi reduce risks, save time, and boost productivity in designing complex integrated circuits.

Challenges in Verifying SoC Connectivity

Microsemi faced challenges in verifying increasingly complex SoCs with over 300,000 gates, 530+ IOs, and other intricate circuitry. Manual verification processes are error-prone, time-consuming, and prone to missing issues, which can lead to costly redesigns.

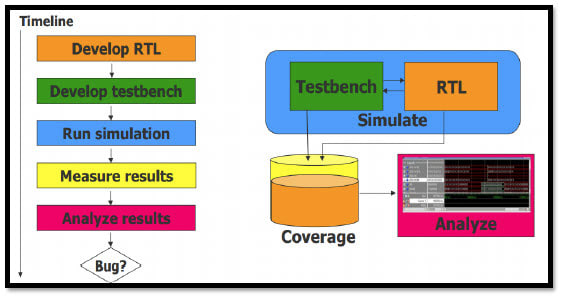

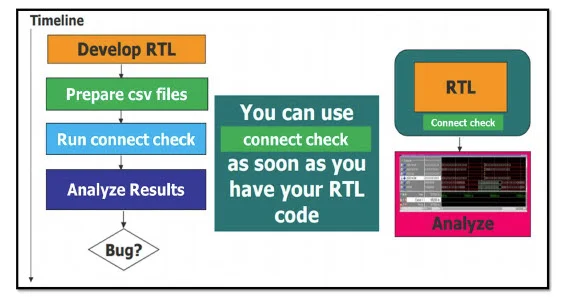

Figure 1: The simulation process (top) requires more effort, steps, and time, and provides less corner-case coverage compared to the Formal Connectivity Check process (bottom)

Figure 1: The simulation process (top) requires more effort, steps, and time, and provides less corner-case coverage compared to the Formal Connectivity Check process (bottom)

Solution and Benefits of Questa Formal Connectivity Check

Microsemi implemented Questa Formal Connectivity Check to verify connectivity, minimizing risks and improving productivity. This tool offers several advantages:

- Comprehensive Analysis: Identifies numerous corner cases that are difficult to catch through simulation.

- Simple Setup: No need for testbenches or deep knowledge of formal verification.

- Shorter Runtime: Enhances verification efficiency and simplifies error detection with software feedback.

- Automatic Assertion Generation: Reduces the need to manually write and debug assertions.

- Easy Debugging: Errors are highlighted with clear counterexamples, shortening debugging time.

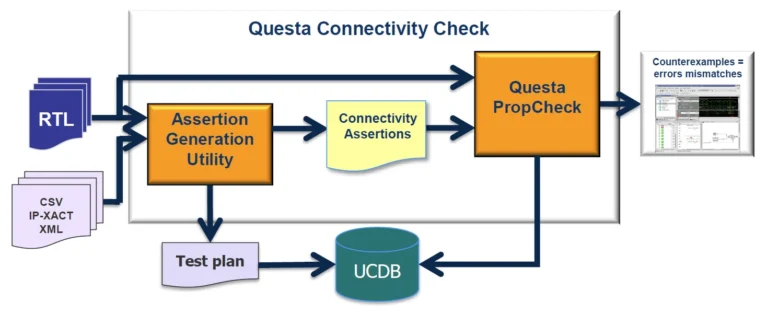

Figure 2: The connectivity verification process of Microsemi’s SoC Division

Figure 2: The connectivity verification process of Microsemi’s SoC Division

Automated Connectivity Verification Process

The process includes eight main steps:

- Step 1: Compile the design.

- Step2: Automatically generate assertions from the RTL code and connectivity specifications.

- Step 3-4: Compile and run formal analysis for the assertions.

- Step 5-8: Create a test plan, review, and debug results using Questa’s GUI.

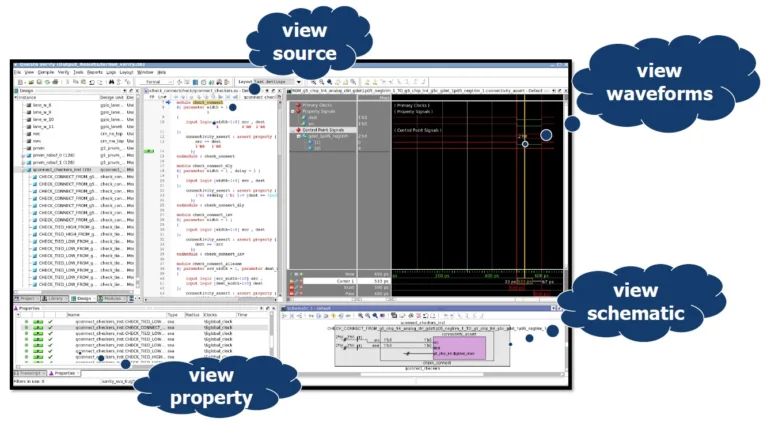

Figure 3: Using Questa GUI, waveforms guide you directly to the root cause

Figure 3: Using Questa GUI, waveforms guide you directly to the root cause

Results and Real-World Evidence

Microsemi used this tool to verify design blocks, system clusters, and full-chip levels. Through this process, they uncovered critical issues such as:

- Incorrect source-to-destination connections.

- Misaligned bit mapping.

- Broken connections.

Notably, the tool also identified errors in the analog domain that simulation could not detect. This is especially crucial when working with product variants.

Conclusion

Microsemi concluded that using formal tools like Questa Formal Connectivity Check is indispensable for early and effective error detection. This tool outperforms traditional simulation methods in terms of comprehensiveness, ease of setup, and time savings, helping Microsemi lower costs and accelerate time-to-market.

(Source: Siemens)

Read more:

Contact us for free and detailed advice: