Ngày 2 tháng 2 tại Hà Nội. Với mục tiêu chia sẻ phương pháp và công nghệ giúp giảm thời gian xử lý lỗi và tối ưu hóa quy trình xác thực thiết kế chip bán dẫn (IC) trước khi sản xuất, VBTECH phối hợp cùng với FPT tổ chức Calibre Workshop: “Rút Ngắn Thời Gian Xử Lý, Đơn Giản Hóa Công Việc – Tăng Tốc Đưa Sản Phẩm Ra Thị Trường” tại Vietnam Semiconductor Innovation Center (VSIC).

Sự kiện thu hút sự tham gia của đông đảo kỹ sư thiết kế IC, kỹ sư backend, kỹ sư xác minh vật lý cùng các quản lý kỹ thuật và quản lý đến từ FPT, Viettel và các doanh nghiệp trong lĩnh vực bán dẫn.

Phương pháp giúp đơn giản hóa và tăng tốc quy trình thiết kế

Chuyên gia cấp cao của Siemens, ông Brad Pu, Giám đốc Kỹ thuật Ứng dụng Calibre khu vực Đài Loan và Đông Nam Á -)với hơn 20 năm kinh nghiệm trong lĩnh vực xác minh vật lý, từng làm việc tại các foundry bán dẫn hàng đầu, đã chia sẻ nhiều kinh nghiệm thực tế trong việc tối ưu hóa quy trình xác minh thiết kế IC và sign-off trước tape-out.

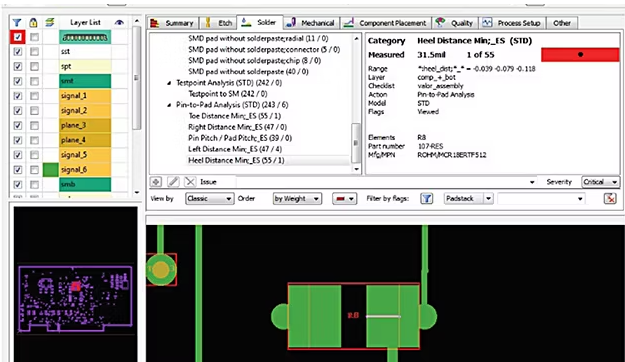

Trong bối cảnh thiết kế vi mạch ngày càng phức tạp, kích thước thiết kế lớn và áp lực rút ngắn thời gian đưa sản phẩm ra thị trường (Time-to-Market) ngày càng cao, sự kiện tập trung giới thiệu các giải pháp trong Siemens EDA Calibre – bộ công cụ xác minh vật lý (Physical Verification) được xem là chuẩn sign-off của ngành bán dẫn, hiện đang được sử dụng rộng rãi tại các công ty thiết kế chip và xưởng đúc trên toàn cầu nhằm hỗ trợ các doanh nghiệp kiểm soát quá trình thiết kế chip tốt hơn nhằm tăng tốc đưa sản phẩm ra thị trường

Một số phương pháp giúp đơn giản hóa và tăng tốc quy trình backend sign-off đã được chuyên gia chia sẻ tại sự kiệnbao gồm:

- Kiểm tra luật thiết kế sớm (Design Rule Check – DRC Recon / Shift-Left Verification) nhằm phát hiện lỗi từ giai đoạn đầu của thiết kế.

- Kiểm tra theo thời gian thực trong quá trình thiết kế (Calibre RealTime – In-Design Checking), cho phép kỹ sư sửa lỗi ngay khi xây dựng layout.

- Tự động hóa xử lý các lỗi đã được chấp nhận (Calibre Auto-Waivers) nhằm giảm thời gian phân tích và debug lặp lại.

- Tối ưu hóa xử lý song song và tài nguyên tính toán (Calibre MTFlex) để tăng tốc các tác vụ DRC và LVS.

- So khớp layout và sơ đồ mạch sớm (LVS Recon SI/CMP) nhằm giảm rủi ro ở giai đoạn sign-off cuối.

- Tăng khả năng sản xuất và hiệu suất yield (Calibre Yield Enhancer – SmartFill) thông qua giải pháp điền kim loại thông minh.

- Kiểm tra độ tin cậy điện – vật lý (Calibre PERC) và phân tích toàn vẹn nguồn, EM/IR (mPower) để đảm bảo độ bền và độ tin cậy của chip.

- Ứng dụng trí tuệ nhân tạo trong phân tích lỗi (Calibre Vision AI) giúp xác định nguyên nhân gốc và rút ngắn thời gian debug.

Giá trị mang lại

Calibre Workshop đã mang đến những kiến thức thiết thực, kinh nghiệm thực tế cùng những giải pháp tối ưu hỗ trợ thiết kế IC để đơn giản hóa công việc, rút ngắn thời gian xử lí và đảm bảo sự chính xác của thiết kế trước khi sản xuất nhằm tăng tốc đưa sản phẩm ra thị trường. Không chỉ thế, kiện còn mang lại cho người tham dự cái nhìn toàn diện về cách các doanh nghiệp có thể giảm số vòng lặp xác minh, tối ưu nguồn lực kỹ sư và hạ tầng tính toán, đồng thời nâng cao chất lượng thiết kế IC trước khi đưa vào sản xuất.

Calibre Workshop là một sự kiện ý nghĩa, cơ hội quý báu để các kỹ sư Việt Nam được trao đổi và kết nối với kỹ sư và chuyên gia trong lĩnh vực bán dẫn, từ đó mở rộng góc nhìn thực tiễn và ứng dụng vào quá trình làm việc thực tế tại doanh nghiệp. Đây cũng là một trong các hoạt động mà Siemens EDA hỗ trợ cộng đồng tại Việt Nam tiếp cận những công nghệ và quy trình tiên tiến, góp phần nâng cao năng lực thiết kế, tăng khả năng cạnh tranh của ngành bán dẫn trong nước, đáp ứng yêu cầu ngày càng cao của ngành bán dẫn toàn cầu.

Tham khảo thêm:

Liên hệ với Vietbay để được tư vấn trực tiếp