Tích hợp không đồng nhất đã biến đổi thiết kế IC của các thiết bị phức tạp, giúp các kỹ sư có thể nhanh chóng và tiết kiệm chi phí tạo ra hệ thống trong gói (System-in-Package – SiP) tiên tiến bằng cách kết hợp IP của bên thứ ba vào chiplet. Công nghệ này mang lại nhiều lợi ích như hiệu suất cao hơn, tiết kiệm năng lượng, khả năng mở rộng, linh hoạt và hiệu quả về chi phí.

Tuy nhiên, chuyển đổi sang thiết kế 2.5D/3D IC không hề đơn giản. Các công cụ và phương pháp thiết kế hiện có vốn được phát triển cho các thiết bị nguyên khối (monolithic devices), tập trung vào từng cấp độ thiết bị riêng lẻ. Vì vậy, chúng không đủ khả năng tối ưu hóa hoàn toàn tiềm năng của tích hợp chiplet.

Tối ưu hóa đồng bộ công nghệ ở cấp hệ thống (STCO)

Tích hợp không đồng nhất đòi hỏi sự chuyển dịch sang phương pháp tối ưu hóa đồng bộ công nghệ ở cấp hệ thống (System-Level Technology Co-Optimization – STCO).

Các nhà thiết kế IC và gói đóng gói giờ đây không thể bỏ qua các yếu tố về công suất, hiệu suất, diện tích, chi phí và độ tin cậy trên toàn bộ các thành phần, bao gồm silicon, package, interposer và PCB. Một quyết định nhỏ ở một cấp độ có thể ảnh hưởng chuỗi domino đến các cấp độ khác.

Do đó, các công cụ và phương pháp thiết kế hiện tại cần phải hỗ trợ quá trình ra quyết định phức tạp này.

Xác định hàng triệu kết nối bump – bằng bảng tính?

Một trong những thách thức lớn nhất là xác định danh sách kết nối (netlist). Khi thiết kế một hệ thống, mỗi thành phần phải được kết nối với nhau. Hiện nay, các thiết kế có hàng trăm nghìn kết nối là điều phổ biến, và công nghệ hybrid bonding thậm chí còn tạo ra nhiều kết nối hơn nữa.

Thông thường, các kết nối này được quản lý bằng bảng tính, trong đó mỗi kết nối được xác định riêng lẻ. Cách tiếp cận này tốn nhiều công sức, dễ xảy ra lỗi, đặc biệt là với các công nghệ băng thông rộng như HBM.

Giải pháp dựa trên bảng tính, ngay cả khi sử dụng macro tùy chỉnh, không thể mở rộng để xử lý hàng trăm nghìn hoặc hàng triệu bump kết nối.

Vì vậy, các nhà thiết kế substrate đang chuyển sang phương pháp thiết kế dựa trên ngôn ngữ lập trình để giải quyết vấn đề kết nối hệ thống. Sử dụng Verilog RTL với ký hiệu bus notation giúp tăng hiệu quả và giảm lỗi so với việc định nghĩa kết nối thủ công bằng bảng tính hoặc viết macro tùy chỉnh trong Excel.

Thực tế, vai trò của các nhà thiết kế đang thay đổi, tập trung nhiều hơn vào nhiệm vụ tích hợp hệ thống. Họ cần hợp tác với nhiều bên liên quan – những người đang phát triển nội dung của họ đồng thời với quá trình thiết kế package hoặc interposer. Mục tiêu của sự hợp tác này là đảm bảo thiết kế đúng về mặt điện và vật lý, đồng thời hoạt động theo đúng mục đích.

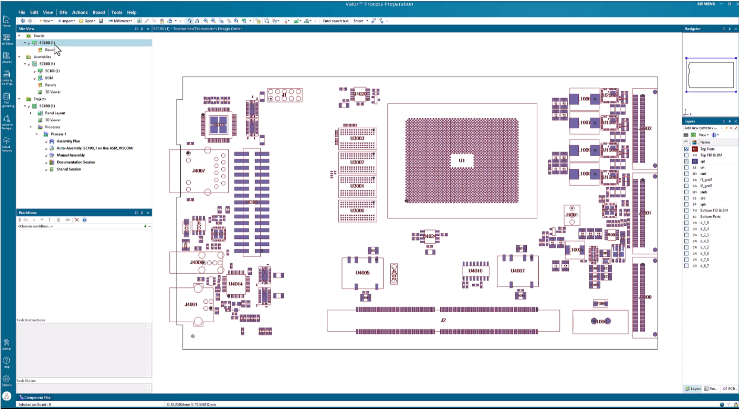

Xây dựng bản sao số (digital twin) của 3D IC trong một môi trường tích hợp

Hiện nay, các công cụ thiết kế không chỉ cần xử lý từng nhiệm vụ riêng lẻ (như xác định netlist) mà còn phải hỗ trợ tích hợp nhiều lĩnh vực song song, tất cả đều đóng góp vào hệ thống cuối cùng.

(Nguồn: Siemens)

Tham khảo thêm:

Liên hệ với Vietbay để được tư vấn: