Chiplet đang cách mạng hóa ngành công nghiệp bán dẫn, cho phép đạt được mức độ tích hợp, hiệu suất và tính linh hoạt chưa từng có. Bằng cách chia nhỏ các thiết kế phức tạp thành các “chiplet” chuyên biệt, các nhà thiết kế có thể khắc phục những hạn chế trong sản xuất, kết hợp và tương thích công nghệ, đồng thời rút ngắn thời gian đưa sản phẩm ra thị trường.

Nhưng có một rào cản quan trọng thường bị bỏ qua: làm thế nào để đảm bảo rằng các chiplet khác biệt này, thường đến từ các xưởng đúc và nút xử lý khác nhau, sẽ hoạt động hoàn hảo khi được tích hợp vào một gói nâng cao?

Nếu bạn là nhà thiết kế đóng gói, kiến trúc sư cấp hệ thống hoặc kỹ sư thiết kế IC làm việc trên các sản phẩm dựa trên chiplet, bạn sẽ hiểu rõ thách thức này. Các phương pháp xác minh IC truyền thống, được thiết kế cho chip đơn khối, đơn giản là không thể đáp ứng được nhiệm vụ này.

Khoảng trống trong xác minh: Tại sao các phương pháp truyền thống lại không hiệu quả

Vấn đề cốt lõi nằm ở “khoảng trống xác minh” đáng kể trong đồng thiết kế IC-package:

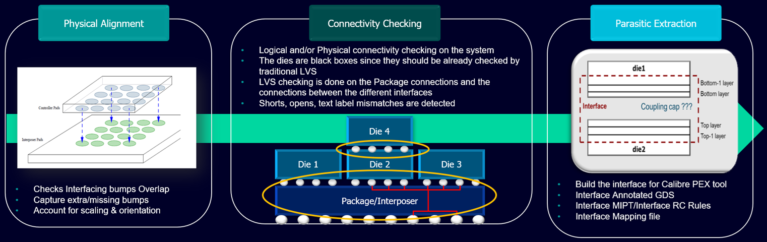

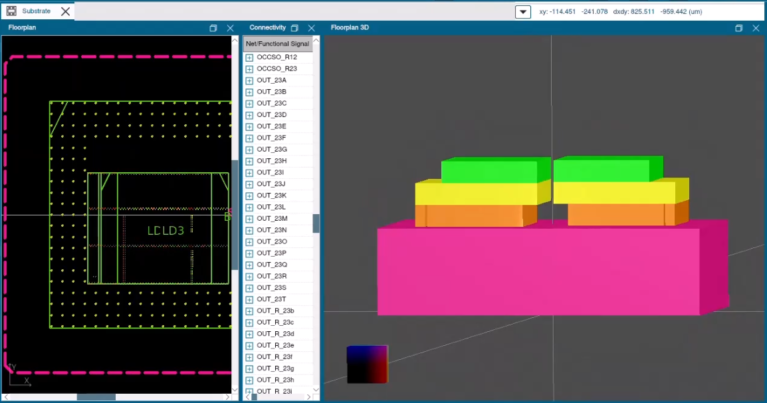

Các giả định 2D trong một thế giới 3D: Các công cụ xác minh vật lý hiện tại dựa trên các định dạng như GDSII, vốn chỉ suy luận được mối quan hệ theo chiều dọc. Điều này không hiệu quả khi có nhiều chip (die) được xếp chồng hoặc đặt cạnh nhau với kết nối phức tạp, nơi mà các hình học trên ‘cùng một lớp’ thực chất có thể bị dịch chuyển theo chiều dọc.

Không nhất quán trong ánh xạ lớp: Các chiplet đến từ nhiều foundry khác nhau, mỗi nơi lại có quy ước ánh xạ lớp riêng. Điều được gọi là ‘metal1’ ở một foundry có thể hoàn toàn khác ở một foundry khác, dẫn đến sự hiểu sai và lỗi.

Thiếu LVS thực sự ở cấp độ package: Các công cụ Layout Versus Schematic (LVS) truyền thống dựa vào netlist kiểu SPICE chi tiết đến mức transistor. Trong khi đó, các công cụ thiết kế package không hoạt động ở mức độ chi tiết này, và SPICE lại quá cồng kềnh để mô tả kết nối trong package. Điều này tạo ra một khoảng trống trong việc xác minh tính kết nối điện trên toàn bộ hệ thống lắp ráp.

Gia tăng rủi ro và chi phí: Không có quy trình xác minh chính thống và lặp lại được, các nhà thiết kế buộc phải dựa vào những phương pháp không nhất quán, làm tăng nguy cơ phải thiết kế lại tốn kém, trễ tiến độ và thậm chí dẫn đến lỗi khi sản phẩm đã ra thị trường.

Thế hệ package tiên tiến mới, như Fan-Out Wafer Level Packages (FOWLP), càng làm mờ ranh giới giữa die và package, đòi hỏi một quy trình đồng thiết kế và xác minh thống nhất.

Mở khóa xác minh package tiên tiến

Bài viết này chỉ là cái nhìn thoáng qua về những thách thức và giải pháp quan trọng trong việc tích hợp chiplet vào các nền tảng đóng gói tiên tiến. Toàn bộ câu chuyện, bao gồm phương pháp luận và quy trình chi tiết, có sẵn trong bộ sách điện tử toàn diện của chúng tôi, do Keith Felton, Giám đốc marketing sản phẩm IC Packaging biên soạn.

Nguồn: Siemens)

Tham khảo thêm:

Liên hệ với Vietbay để được tư vấn: