The best way to create a System on a Chip is with design IP. Your project may have a memory controller and PHY that takes commands from the system bus and turns them into the detailed pin wiggles for devices such as DDR. How do you then check that your chip works with the design IP? You need to check that your memory subsystem works with the DDR protocol, but who has time to become an expert? The best way to verify your design is with Verification IP, or VIP.

Siemens Questa Memory Verification IP (QVIP) has a wide range of DRAM and Flash memories. QVIP works with both SystemVerilog and VHDL designs, and easily integrates into a UVM testbench.

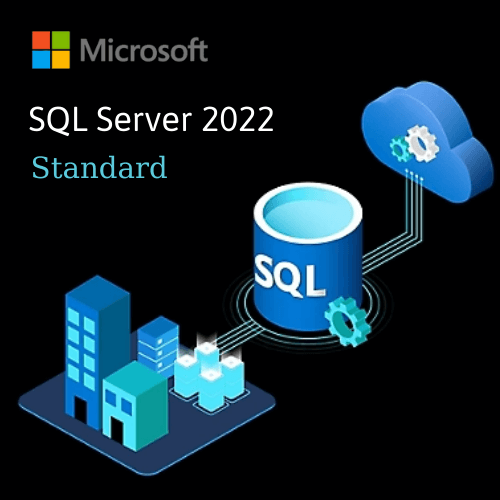

Verify your memory subsystem

What is the memory subsystem? There is a controller with a bus interface such as AXI, AHB, OCP, etc. This communicates with the PHY through a DFI interface, which drives the memory devices through DDR interface. There may be additional features such as continuous flow of commands and data over the memory interface, multi-port arbitration functionality, memory coherency, and more. With QVIP, you can model the bus controller and the DRAM devices.

You can verify read and write transactions in your controller with Questa Memory Verification IP which supports a range of DDR speed grades and manufacturers. Additionally, you can simulate real world conditions by verifying that your memory subsystem IP correctly performs memory training and operates under low power conditions.

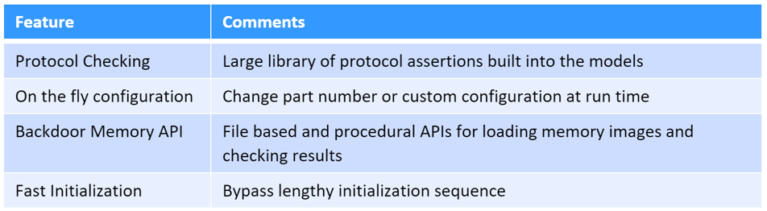

Benefits of QVIP Memory Models

QVIP Integration Flow

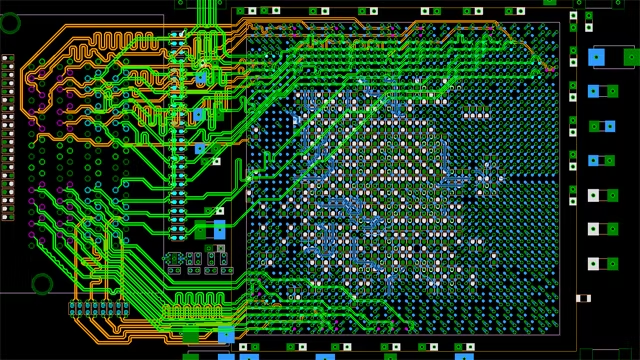

You can easily integrate Questa Memory Verification IP DDR models with your design and start simulating in a few hours. Here are the four steps to connect QVIP to your testbench and verify your system. You can do the first two with the QVIP Configurator GUI.

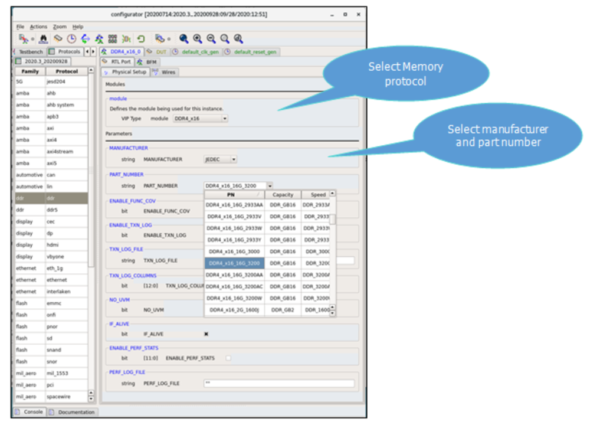

- Connect & configure RTL + QVIP: Configurator reads your top netlist and creates a schematic symbol. You connect it to QVIP blocks such as a DDR VIP, AXI Master, plus clock and reset. The QVIP code, including the bus functional model and SystemVerilog Assertions, is inside a single module, which reduces the number of connections. Here you can see selecting a memory model based on type and manufacturer.

- Generate compile & sim scripts: QVIP supports all major SystemVerilog and VHDL simulators.

- Simulate & debug: Simulate the test and leverage debugging features.

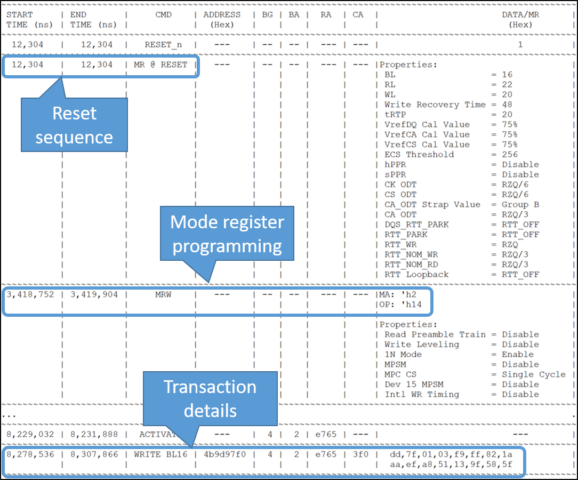

The transaction logger creates a text file that has memory transfers, mode registers and assertions.

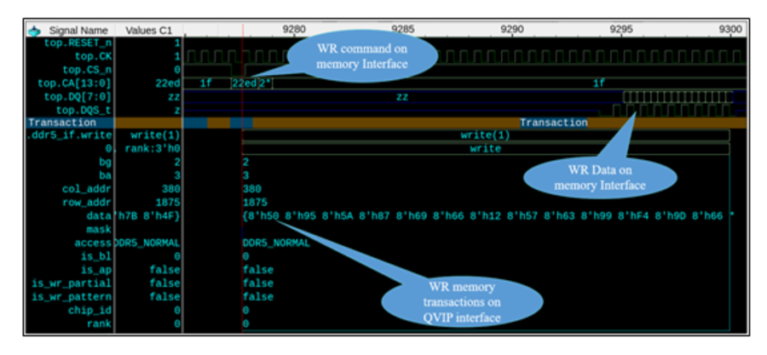

The transaction streams viewer displays transactions in the wave and co-relates pin-level activity with memory transactions.

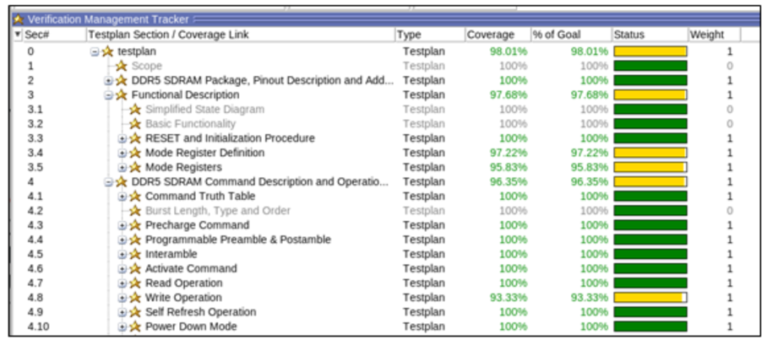

- Analyze Functional Coverage: you can measure verification progress and quickly see what areas need further testing. The covergroups are based on the JEDEC standard. Functional Coverage modules are unencrypted and extendable for custom use. You can view the Coverage report either in HTML or text formats.

Where to start?

Do you already have a UVM testbench, and want to add a Questa Memory Verification IP agent? Do you want to see alternative topologies with masters, slaves, and monitors? QVIP comes with an extensive library of ready-to-run examples that you can explore.

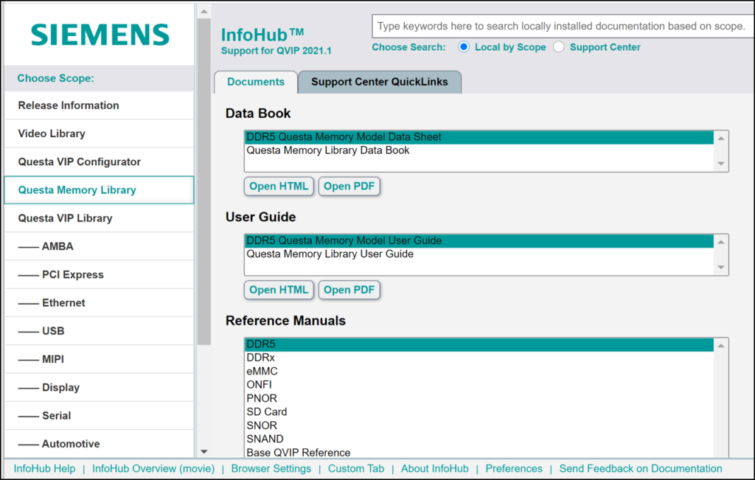

Questa Memory Verification IP has User Guides for every protocol that walk you through the steps to verify your design. Need more details on a class, property, or method? The QVIP reference manuals have in-depth explanations of the QVIP bus functional model and SystemVerilog Assertions. There are even several video tutorials that walk you through popular topics such as injecting errors and debugging with Visualizer.

(Source: Siemens)

For more information, please contact: