Cách tốt nhất để tạo một System on a Chip (Soc) là với thiết kế IP. Dự án của bạn có thể có bộ điều khiển bộ nhớ và PHY nhận các lệnh từ bus hệ thống và biến chúng thành các pin chi tiết cho các thiết bị như DDR. Làm thế nào để bạn kiểm tra xem chip của bạn có hoạt động với IP thiết kế không? Bạn cần kiểm tra xem hệ thống con bộ nhớ của bạn có hoạt động với giao thức DDR hay không, nhưng ai có thời gian để trở thành một chuyên gia? Cách tốt nhất để xác minh thiết kế của bạn là sử dụng Verification IP hoặc VIP.

Siemens Questa Memory Verification IP (QVIP) có nhiều loại bộ nhớ DRAM và Flash. QVIP hoạt động với cả thiết kế SystemVerilog và VHDL, đồng thời dễ dàng tích hợp vào testbench UVM.

Xác minh hệ thống con bộ nhớ của bạn

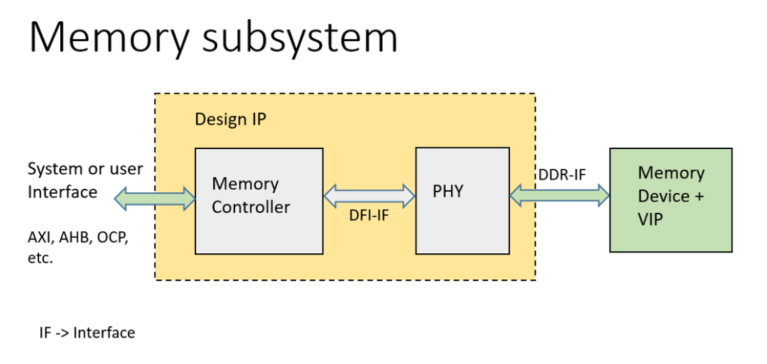

Hệ thống con bộ nhớ là gì? Có một bộ điều khiển với giao diện bus như AXI, AHB, OCP, v.v. Bộ điều khiển này giao tiếp với PHY thông qua giao diện DFI, điều khiển các thiết bị bộ nhớ thông qua giao diện DDR. Có thể có các tính năng bổ sung như luồng lệnh và dữ liệu liên tục qua giao diện bộ nhớ, chức năng phân xử đa cổng, tính nhất quán của bộ nhớ, v.v. Với QVIP, bạn có thể mô hình hóa bộ điều khiển bus và các thiết bị DRAM.

Bạn có thể xác minh các giao dịch đọc và ghi trong bộ điều khiển của mình bằng QVIP hỗ trợ nhiều loại tốc độ DDR và nhà sản xuất. Ngoài ra, bạn có thể mô phỏng các điều kiện trong thế giới thực bằng cách xác minh rằng IP hệ thống con bộ nhớ của bạn thực hiện chính xác việc đào tạo bộ nhớ và hoạt động trong điều kiện năng lượng thấp.

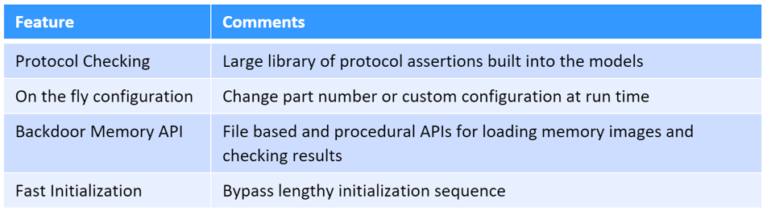

Lợi ích của QVIP Memory Models

Quy trình tích hợp QVIP

Bạn có thể dễ dàng tích hợp các mô hình QVIP DDR với thiết kế của mình và bắt đầu mô phỏng sau vài giờ. Dưới đây là 4 bước để kết nối QVIP với testbench của bạn và xác minh hệ thống của bạn. Bạn có thể thực hiện hai bước đầu tiên với QVIP Configurator GUI.

1. Connect & configure RTL + QVIP

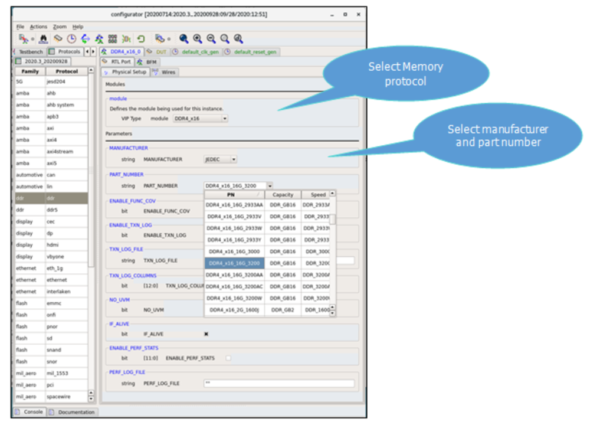

Trình Configurator đọc netlist của bạn và tạo biểu tượng sơ đồ. Bạn kết nối nó với các khối QVIP như DDR VIP, AXI Master, cùng với đồng hồ và thiết lập lại. Mã QVIP, bao gồm mô hình chức năng bus và SystemVerilog Assertions, nằm trong một mô-đun duy nhất, giúp giảm số lượng kết nối. Tại đây, bạn có thể thấy việc chọn kiểu bộ nhớ dựa trên loại và nhà sản xuất.

2. Generate compile & sim scripts

QVIP hỗ trợ tất cả các trình giả lập SystemVerilog và VHDL chính.

3. Simulate & debug

Mô phỏng thử nghiệm và tận dụng các tính năng gỡ lỗi.

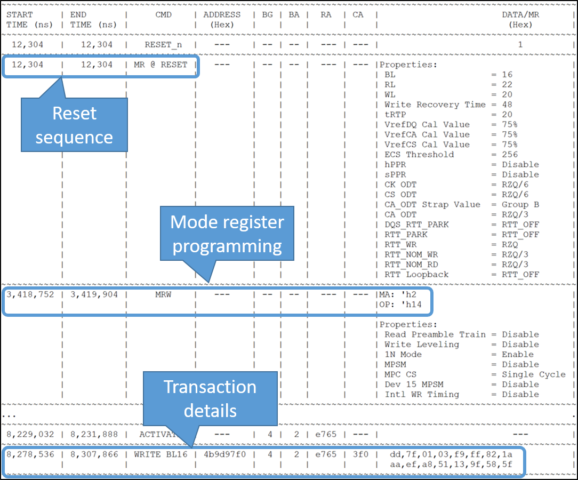

Trình ghi giao dịch tạo một tệp văn bản có chuyển bộ nhớ, chế độ registers và assertions.

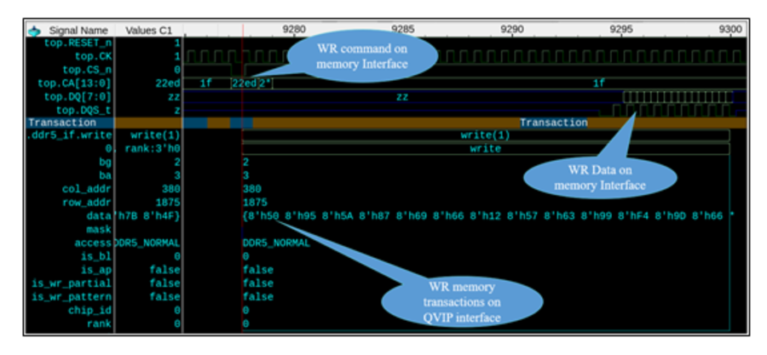

Trình xem luồng giao dịch hiển thị các giao dịch trong wave và co-relates pin-level hoạt động với các giao dịch bộ nhớ.

4. Analyze Functional Coverage

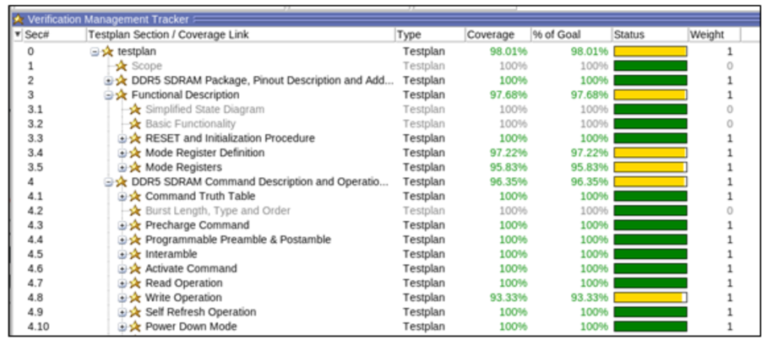

Bạn có thể đo lường tiến độ xác minh và nhanh chóng xem những khu vực nào cần thử nghiệm thêm. Các covergroups dựa trên tiêu chuẩn JEDEC. Các mô-đun Functional Coverage không được mã hóa và có thể mở rộng để sử dụng tùy chỉnh. Bạn có thể xem báo cáo Coverage ở định dạng HTML hoặc văn bản.

Bắt đầu từ đâu?

Bạn đã có testbench UVM và muốn thêm QVIP? Bạn có muốn xem cấu trúc liên kết thay thế với masters, slaves và monitors? QVIP đi kèm với một thư viện phong phú các ví dụ sẵn sàng chạy mà bạn có thể khám phá.

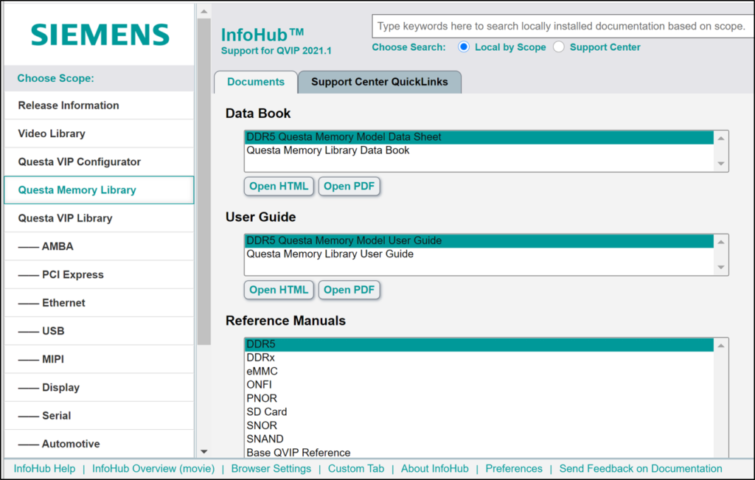

QVIP có User Guides cho mọi giao thức hướng dẫn bạn qua các bước để xác minh thiết kế của bạn.

Để biết thêm thông tin chi tiết, vui lòng liên hệ: