ModelSim simulates behavioral, RTL, and gate-level code – delivering increased design quality and debug productivity with platform-independent compile. Single Kernel Simulator technology enables transparent mixing of VHDL and Verilog in one design.

Key features

ModelSim packs an unprecedented level of verification capabilities into a cost-effective HDL simulator and is ideally suited for the verification of small and medium-sized FPGA designs – especially designs with complex, mission-critical functionality.

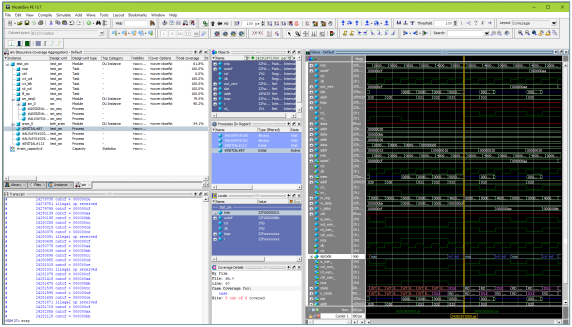

Advanced code coverage

ModelSim’s advanced code coverage capabilities provide valuable metrics for systematic verification. Plus, ModelSim’s ease of use lowers the barriers for leveraging verification resources. All coverage information is stored in the highly efficient UCDB database. Coverage results can be viewed interactively, post-simulation, or after a merge of multiple simulation runs.

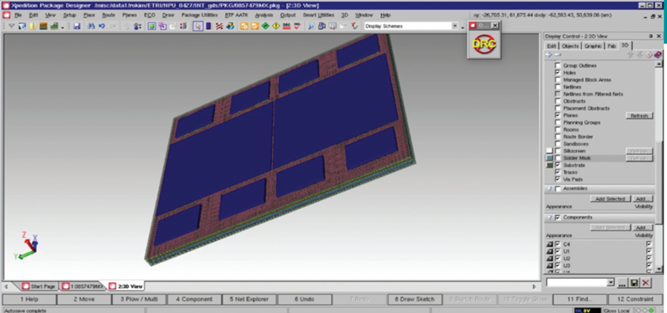

Mixed HDL simulation

Comprehensive support of Verilog, SystemVerilog for Design, VHDL, and SystemC provide a solid foundation for single and multi-language design verification environments. An easy-to-use and unified environment provides FPGA designers the advanced capabilities they need for debugging and simulation.

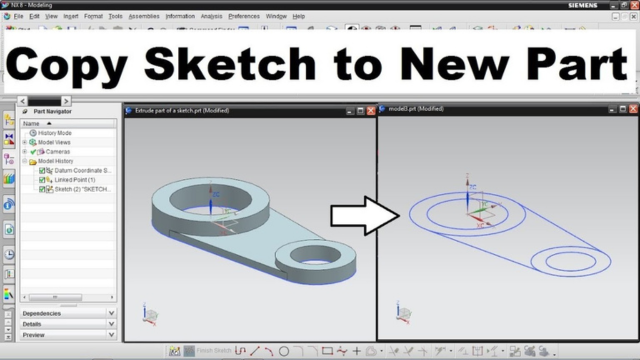

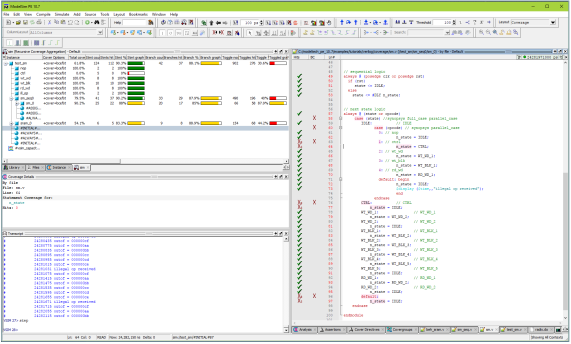

Intuitive debug environment

ModelSim eases the process of finding design defects with an intelligently engineered debug environment that efficiently displays design data for analysis and debug of all hardware description languages. A broad set of intuitive capabilities for Verilog, VHDL and SystemC make it the ideal choice for ASIC and FPGA design.

Source: Siemens

For more information, please contact: