Các nhà thiết kế chip mạch tích hợp (IC) không ngừng nỗ lực để đáp ứng các tiêu chuẩn ngày càng tăng về độ tin cậy và hiệu suất trong lĩnh vực sản xuất chất bán dẫn có nhịp độ nhanh. Giữa những thách thức này, hư hỏng do plasma gây ra (PID) trong oxit cổng, thường được gọi là hiệu ứng ăng-ten, là mối đe dọa đáng kể đối với hiệu suất và độ tin cậy của mạch MOSFET. Mặc dù PID thực sự xảy ra trong quá trình sản xuất vi mạch nhưng nó có thể được giảm thiểu hoặc loại bỏ bằng cách tìm và sửa các mẫu layout nhạy cảm trong giai đoạn thiết kế layout.

Quy tắc thiết kế ăng-ten truyền thống

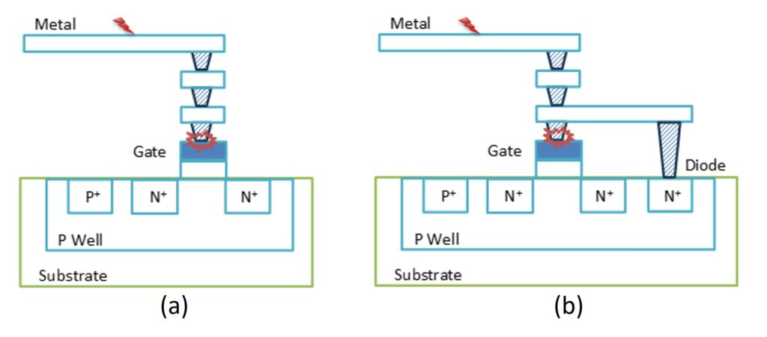

Các quy tắc thiết kế ăng-ten truyền thống kiểm tra từng lớp để biết tỷ lệ diện tích tối đa được phép giữa lớp kim loại và lớp cổng MOSFET được kết nối với cùng một mạng, như trong hình 1(a). Việc bổ sung thiết bị bảo vệ đi-ốt sẽ mở rộng tỷ lệ diện tích tối đa cho phép này, như minh họa trong hình 1(b). Quy trình kiểm tra quy tắc thiết kế truyền thống (DRC) xử lý các hoạt động kiểm tra này một cách dễ dàng và hiệu quả.

Những thách thức về ăng-ten ngày càng tăng trong thiết kế chip IC

Trong những năm gần đây, thiết kế tín hiệu hỗn hợp tương tự (AMS) đã trở nên phổ biến nhờ khả năng tích hợp nhỏ gọn và giảm mức tiêu thụ điện năng. Thiết kế AMS liên quan đến nhiều miền năng lượng tạo ra những thách thức về thiết kế trên nhiều miền. Những thách thức này bao gồm sự tồn tại của các giếng loại P bị cô lập, đã gây ra một thế hệ vấn đề về ăng-ten mới không thể giải quyết hiệu quả bằng cách sử dụng các biện pháp kiểm tra DRC truyền thống:

Rủi ro kết nối

Xác định thời điểm rủi ro thiết lập kết nối giữa bộ điều khiển và bộ thu trước khi thiết lập kết nối bảo vệ tương ứng giữa hai giếng loại P bị cô lập.

Hư hại do sạc

Phát hiện tỷ lệ diện tích mất cân bằng giữa các lớp kim loại và các lớp giếng từ hai giếng loại P bị cô lập.

Miễn trừ kết nối

Phân tích các điều kiện kết nối phức tạp có thể loại bỏ các vi phạm ăng-ten do tỷ lệ diện tích không cân bằng gây ra.

Điốt bảo vệ ngoài ý muốn

Kiểm tra các điốt bảo vệ ngoài ý muốn được hình thành do kết nối, làm tăng tỷ lệ diện tích tối đa cho phép.

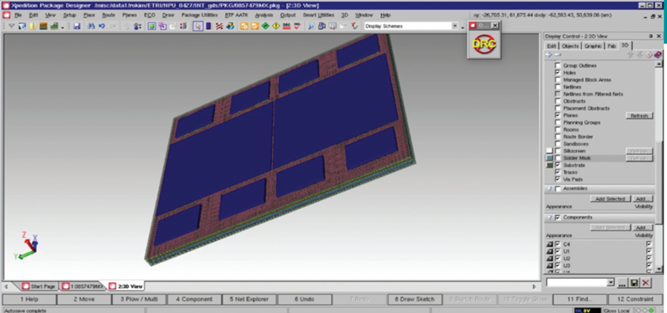

Xác minh ăng-ten dựa trên đường dẫn và tầm quan trọng của nó trong thiết kế chip IC

Việc giải quyết các quy tắc thiết kế ăng-ten phức tạp này đòi hỏi một giải pháp toàn diện để hiểu các thiết bị, khả năng kết nối và đường dẫn điện trong thiết kế vi mạch trong khi tính toán diện tích lớp cổng kim loại và MOSFET. Tin tốt? Nền tảng xác minh độ tin cậy của Siemens EDA Calibre® PERC™ cho phép các nhà thiết kế xác định các đường dẫn quan tâm trong thiết kế chip IC và thực hiện kiểm tra quy tắc ăng-ten phức tạp trên các đường dẫn đó, mang lại sự linh hoạt và hiệu quả.

Mặc dù phương pháp xác minh dựa trên đường dẫn này là cần thiết để giải quyết các quy tắc thiết kế ăng-ten phức tạp và đang phát triển, việc kiểm tra ăng-ten dựa trên DRC truyền thống vẫn là một phần có giá trị của quy trình xác minh. Hai luồng xác minh bổ sung cho nhau, cung cấp phạm vi bao phủ hoàn chỉnh cho cả quy tắc thiết kế ăng-ten truyền thống và nâng cao: Trong giai đoạn thiết kế ban đầu, khi các kết nối chưa hoàn chỉnh, kiểm tra DRC truyền thống có thể được sử dụng để kiểm tra sơ bộ từng cấu trúc liên quan đến ăng-ten. Việc xác minh này đảm bảo rằng các bố cục được xây dựng có tính đến tính năng ngăn chặn PID, giúp giảm nhu cầu sửa lỗi tốn thời gian trong các lần lặp lại sau này. Khi các đường dẫn hình thành trên các giếng loại P bị cô lập, giải pháp dựa trên đường dẫn trở nên không thể thiếu để kiểm tra các quy tắc thiết kế ăng-ten phức tạp hơn.

Nếu bạn là nhà thiết kế chip IC đang bị giảm năng suất do các vấn đề về PID, giải pháp PID dựa trên đường dẫn Calibre PERC có thể hữu ích cho bạn.

Nguồn: siemens

Vietbay – Nhà phân phối ủy quyền của Siemens EDA và với hơn 20 năm kinh nghiệm trong lĩnh vực tư vấn, cung cấp và đào tạo chuyển giao công nghệ, Vietbay cam kết cung cấp giải pháp thiết kế và sản xuất IC và PCB toàn diện với dịch vụ và giá trị gia tăng để giúp cho khách hàng làm chủ công nghệ, phát triển nhanh và bền vững trong thời đại số.

Liên hệ với Vietbay để được tư vẫn miến phí: