Khi các thiết bị điện tử tiêu dùng ngày càng được kết nối, thông minh và tiên tiến, các nhà thiết kế cần các phương pháp mới như IC 3D để giải quyết các hạn chế “nhiều hơn Moore”. Các thiết bị ngày càng phức tạp bao gồm nhiều tính năng hơn và thiết kế mạch điện tử phức tạp hơn, đòi hỏi khả năng xử lý cao hơn. Để đáp ứng những nhu cầu này, các nhà thiết kế cần những phương pháp mới để thiết kế và kết nối chip.

Cùng Vietbay tìm hiểu chi tiết ngay dưới đây nhé!

IC 3D là gì?

IC 3D là một mạch tích hợp ba chiều và đề cập đến sự tích hợp, phương pháp và công nghệ. Các nhóm thiết kế chia nhỏ kiến trúc triển khai nguyên khối truyền thống thành nhiều chip hoặc chiplet chức năng nhỏ hơn được tích hợp bằng gói hiệu suất cao. Các mạch tích hợp 3D này chiếm ít không gian hơn và mang lại hiệu suất cao hơn nhiều so với các công nghệ nguyên khối truyền thống.

Công nghệ dành cho bộ nhớ băng thông cao (HBM) xuất hiện khoảng mười năm trước, nơi có nhiều chip bộ nhớ được xếp chồng lên nhau. Những con chip xếp chồng này cung cấp rất nhiều bộ nhớ với kích thước nhỏ và được tích hợp vào ASIC trên bộ chuyển đổi 2.5D, đây là nơi bắt nguồn của thuật ngữ đó.

IC 3D giải quyết được vấn đề gì?

Ngành công nghiệp bán dẫn đã chứng kiến các nút công nghệ mạch tích hợp dành riêng cho ứng dụng (ASIC) tiên tiến có quy mô đáng kể trong 40 năm qua, bên cạnh hiệu suất cao hơn. Khi chúng ta đạt đến giới hạn của định luật Moore, việc mở rộng quy mô thiết bị trở thành một thách thức. Các thiết bị thu nhỏ với tốc độ chậm hơn, mất nhiều thời gian hơn và chi phí cao hơn nhiều cho công nghệ, thiết kế, phân tích và sản xuất các con chip này.

Có những hạn chế thực tế về mức độ lớn mà bạn có thể tạo ra một thiết bị. Kích thước mặt nạ ảnh và mặt kẻ ô cuối cùng sẽ xác định kích thước tối đa của chip – khoảng 25 đến 27 mm mỗi cạnh. Vì vậy, về mặt vật lý, bạn không thể tạo ra một con chip lớn hơn thế. Vì số lượng bóng bán dẫn đã giảm nên các nhà thiết kế không được hưởng lợi từ sự phức tạp ngày càng tăng bằng cách đặt ngày càng nhiều thiết bị vào một gói duy nhất. Các nhà thiết kế vi mạch 3D không phải đối mặt với những thách thức tương tự.

Sở hữu trí tuệ (IP) hệ thống trên chip (SOC) là các khối xây dựng cơ bản được triển khai trong chip đó. Các loại chức năng khác nhau đòi hỏi công nghệ ASIC rất chuyên dụng. Trong một số trường hợp, nó có thể hạn chế những gì bạn có thể triển khai trong hệ thống vì bạn sẽ cần tất cả IP có sẵn trong cùng một quy trình nếu bạn định tích hợp nó vào một chip duy nhất. Khi chúng tôi sử dụng IC 3D, bạn không còn gặp hạn chế đó nữa. Vì vậy, bạn có thể có được các chiplet thực hiện một chức năng cụ thể, chẳng hạn như sở hữu trí tuệ. Chiplet đó có thể được tối ưu hóa bằng cách sử dụng công nghệ thích hợp nhất cho loại chức năng đó.

IC 3D hoạt động như thế nào?

Vì IC 3D không bị giới hạn về kích thước của một thiết bị nên các nhà thiết kế có thể tạo ra các hệ thống lớn hơn nhiều bằng cách đặt nhiều chip vào một gói. Ý nghĩa của thiết kế nguyên khối đối với các thiết bị điện toán và AI hiệu năng cao sẽ tiếp tục sử dụng các công nghệ nguyên khối. Nhưng họ có thể tận dụng sự phân chia này bằng cách chia thiết kế thành một bộ chip nhỏ hơn. Nhưng nhìn chung, nếu bạn có thể nhét mọi thứ bạn cần vào một con chip duy nhất, bạn sẽ có được chi phí đơn vị thấp nhất và hiệu suất cao nhất. Khi các nhà thiết kế bắt đầu gặp phải những hạn chế, đó là lúc công nghệ 2.5D hoặc 3D có thể mở rộng khả năng của họ.

Trong nhiều năm, các nhà thiết kế đã tạo ra các mô-đun nhiều chip (MCM). Họ đặt một hoặc nhiều chip ASIC vào một gói duy nhất và kết nối chúng với các công nghệ đóng gói truyền thống. MCM là một công nghệ rất trưởng thành nhưng cũng có một số hạn chế. IC 3D được thúc đẩy nhiều hơn bởi công nghệ đóng gói tiên tiến để tích hợp các chiplets. Chiplet là một ASIC được thiết kế để tích hợp với các chiplet khác trong một gói. Những chiplets này có hai loại:

2D (hoặc 2.5D)

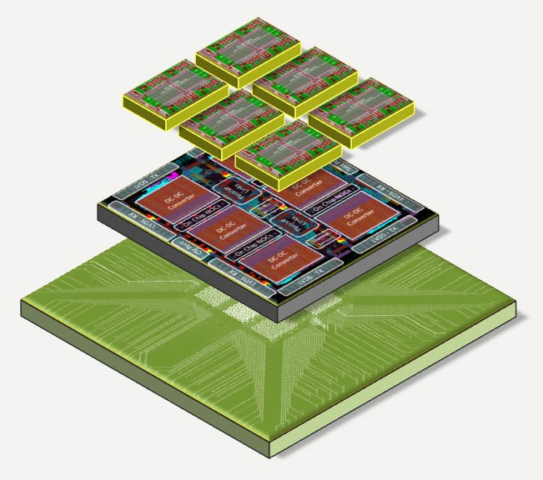

Tích hợp hai chip trên một bộ chuyển mạch duy nhất và kết nối các chiplet đó trên bộ chuyển mạch đó bằng kết nối kim loại.

3D

Xếp chồng khuôn liên quan đến việc xếp chồng các chip bộ nhớ hoặc cảm biến lên một chip khác (như bộ nhớ). True 3D là một công nghệ rất tiên tiến giúp chia ASIC thành hai chip và xếp chồng chúng lên nhau.

Không có lựa chọn nào mà nhóm thiết kế chất bán dẫn có sẵn phải đối mặt với một số thách thức nguyên khối dường như là một giải pháp “một kích thước phù hợp cho tất cả” hoặc hoàn chỉnh.

IC 3D có gì khác biệt so với các công nghệ khác?

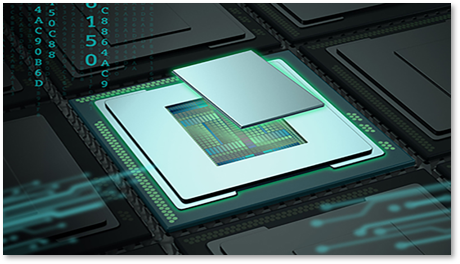

Sự khác biệt giữa MCM truyền thống là công nghệ đóng gói – có thể là 2D hoặc 3D. Một điểm khác biệt chính là sự kết nối giữa các thiết bị ở cấp độ silicon. Các dây ngắn hơn và mỏng hơn nhiều, làm cho điện trở và điện dung chậm hơn đáng kể và cho phép nhiều kết nối hơn giữa các chip.

Trên thực tế, công nghệ đóng gói 3D hoặc 2D cho phép tăng hiệu suất với độ phức tạp cao hơn với nhiều kết nối hơn – cho phép các nhà thiết kế xây dựng các hệ thống với diện tích nhỏ hơn nhiều bên trong một gói duy nhất.

Các nhà thiết kế có thể phân rã hệ thống thành các chức năng được triển khai dưới dạng chip nhỏ hơn hoặc chiplets thay vì đặt mọi thứ vào một thiết bị ASIC đồng nhất duy nhất.

Sự khác biệt khác ở đây là các nhà thiết kế hệ thống hiện có nhiều tùy chọn hơn để triển khai các thiết bị phức tạp của họ và tận dụng một số lợi ích vốn có của 2.5D và 3D. Vì vậy, nó cung cấp cho họ nhiều lựa chọn hơn trong việc phát triển hệ thống của mình, tận dụng một số lợi ích do các công nghệ này mang lại.

Chúng ta phải đối mặt với những thách thức gì với IC 3D?

Bây giờ chúng ta đã biết tích hợp IC 3D là gì và nó khác với các công nghệ đóng gói tích hợp tiên tiến khác như thế nào, chúng tôi biết có một số thách thức khi chuyển sang IC 3D:

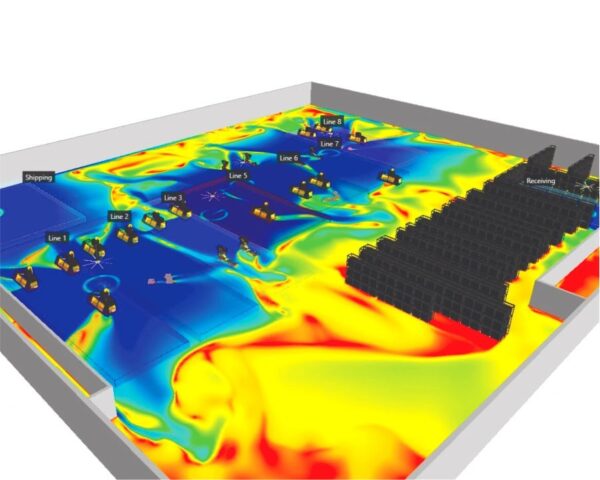

Quản lý nhiệt

Một thiết bị ASIC truyền thống sử dụng một cấu hình nguồn đơn rất đơn giản. Trong gói IC 3D, các nhà thiết kế phải quản lý cấu hình năng lượng nhiệt của nhiều chip. Các nhà thiết kế cũng cần hiểu rõ sự tương tác nhiệt giữa các thành phần khác nhau để đảm bảo gói đáp ứng được yêu cầu về nhiệt của thiết bị.

Phân tích ứng suất cơ học

Khi bạn xếp khuôn hoặc xếp chồng một tấm silicon lớn lên trên một chất nền hữu cơ, hệ số giãn nở nhiệt giữa các vật liệu là khác nhau nên chúng sẽ uốn cong và uốn cong khác nhau. Ứng suất cơ học tiềm ẩn đối với các kết nối giữa các thiết bị đó có thể gây ra lỗi và các vấn đề về độ tin cậy. Vì mỗi thiết kế là duy nhất nên các nhà thiết kế nên thực hiện phân tích bằng các mô phỏng cơ học để lập mô hình ứng suất đó.

Thiết kế và phân tích mạng lưới phân phối điện

Các nhà thiết kế gói phải xem xét rằng nhiều chiplet có thể có các yêu cầu về điện áp, nguồn điện và tiếng ồn khác nhau.

Khả năng kiểm tra

Có lẽ vấn đề phức tạp nhất đối với IC 3D là kiểm tra, thường là quy trình gồm hai bước cho các thiết bị đơn lẻ. Hai loại thử nghiệm là thử nghiệm ở cấp độ wafer và thử nghiệm cuối cùng sau khi chip được đóng gói. Có nhiều chip bên trong các thiết bị 2.5D và 3D. Các nhà sản xuất có thể đã kiểm tra wafer chúng trước khi giao cho các nhà tích hợp hệ thống nhưng vẫn yêu cầu kiểm tra giao diện giữa các chip và kiểm tra lại các thiết bị đóng gói.

Giải pháp thiết kế IC Calibre trong xác minh IC

Các giải pháp thiết kế IC Calibre là dẫn đầu trong ngành về xác minh IC, cung cấp nền tảng EDA xác minh IC hoàn chỉnh và tối ưu hóa DFM giúp tăng tốc thiết kế từ khâu sáng tạo đến sản xuất, giải quyết tất cả các yêu cầu sign-off.

Top 5 giải pháp thiết kế IC Calibre:

- Calibre xác minh vật lý

- Calibre xác minh mạch

- Calibre xác minh độ tin cậy

- Calibre thiết kế cho sản xuất

- Calibre giao diện

Tìm hiểu chi tiết sản phẩm ngay tại đây

Nguồn: Siemens

Tham khảo thêm:

Vietbay – Nhà phân phối ủy quyền của Siemens EDA và với hơn 20 năm kinh nghiệm trong lĩnh vực tư vấn, cung cấp và đào tạo chuyển giao công nghệ, Vietbay cam kết cung cấp giải pháp thiết kế và sản xuất IC và PCB toàn diện với dịch vụ và giá trị gia tăng để giúp cho khách hàng làm chủ công nghệ, phát triển nhanh và bền vững trong thời đại số.

Liên hệ với Vietbay để được tư vẫn miến phí: