Is your FPGA design flow ready for the new class of designs targeting the latest complex FPGAs? Are you struggling with point tools that don’t work together? Are you able to meet your QoR goals in the desired budget? Can your PCB and FPGA teams collaborate to achieve the overall system constraints?

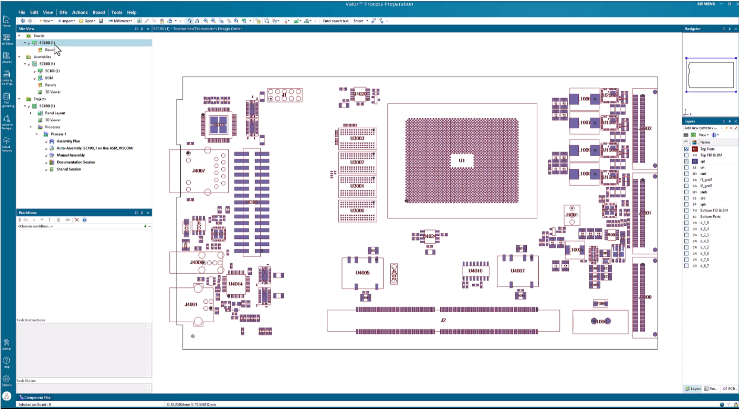

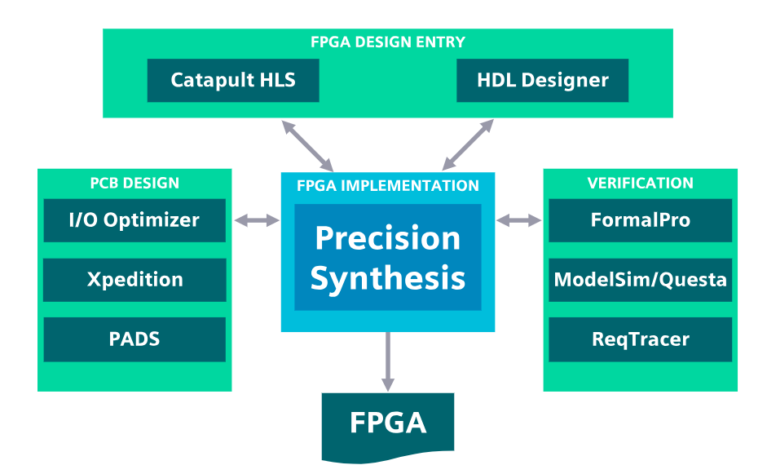

Siemens EDA’s Complete FPGA Design Flow

Siemens EDA’s FPGA design solutions deliver an integrated FPGA design entry, synthesis, verification, equivalence checking, and PCB design platform that speeds up FPGA designs from creation to board, meeting design QoR goals and system constraint requirements.

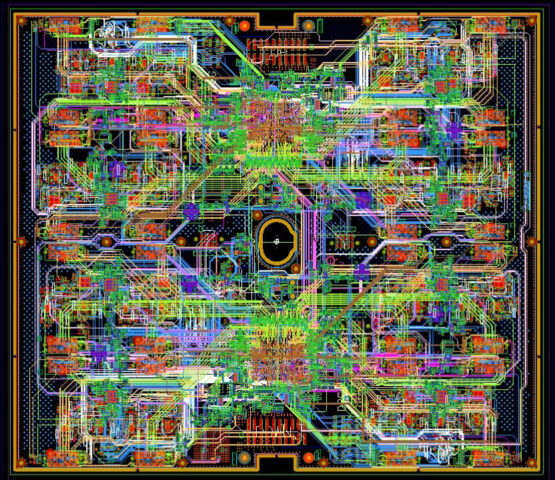

New Class of FPGA Designs & Methodologies

FPGAs are increasingly being used in fast-evolving market segments (such as 5G, ML and AI) and safety-critical/high-reliability designs. This class of designs requires use of newer methodologies such as HLS or SEE mitigation. Additionally, it poses challenges to debug and verify these large designs.

Safe & Reliable FPGA Design

For safety-critical designs, Precision Hi-Rel provides fail-safe mechanisms (detect, mask, mitigate) to reduce the probability of soft error occurrence and propagation due to radiation, vibration or other environmental conditions.

Accelerate C++/SystemC Design on FPGAs

Tight integration and better arithmetic operator estimation between Catapult and Precision FPGA Synthesis tool are critical in achieving optimal QoR and faster time to design closure for C++/SystemC designs.

Is Gate-Level Simulation too Slow?

Integration between FormalPro and Precision FPGA Synthesis tool ensures orders of magnitude faster verification of synthesized gate-level netlist against golden RTL designs with complex DSP and RAMs.

Source: siemens

Learn more:

- FPGA/PCB co-design with PADS Professional Premium

- ModelSim – ASIC and FPGA debugging and verification software

Contact us for free and detailed advice